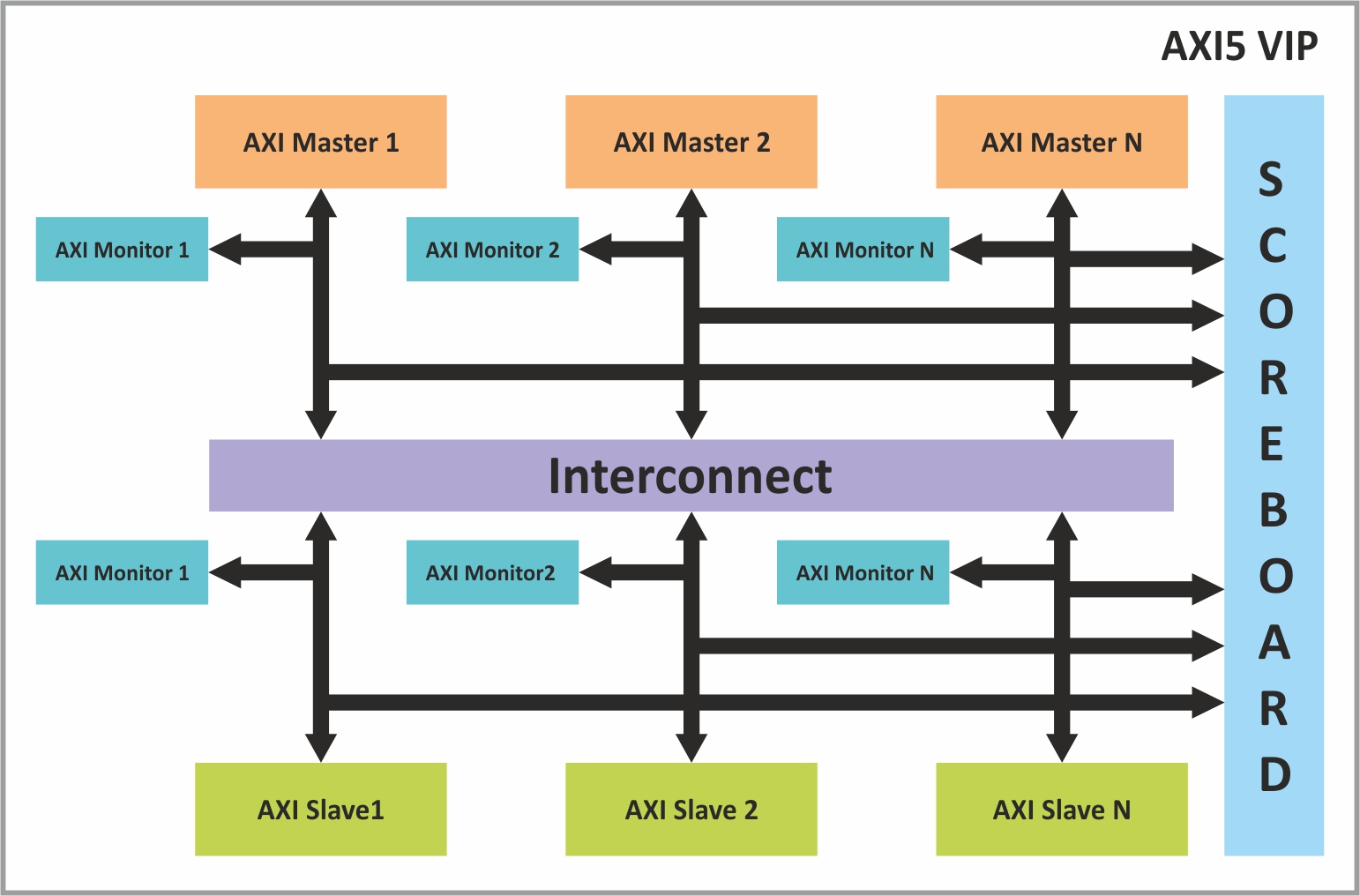

AMBA AXI5 Verification IP

Truechip's AMBA AXI5 Verification IP provides an effective & efficient way to verify the components interfacing with the AMBA® AXI5 bus of an IP or SoC. Truechip's AMBA AXI5 VIP is fully compliant with standard AMBA® AXI5 specifications from ARM. This VIP is a lightweight VIP with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- AXI5 VIP is Compliant with the latest ARM™ AMBA AXI5 & AXI5 lite.

- It is also compatible with AXI3, AXI4 Protocol Specification v2.0 referred to as AXI4 and AXI4-Lite.

- Supports Unique ID feature for both read and write transactions.

- Supports MTE(Memory Tagging Extension) feature to detect memory safety violations.

- Supports Read data chunking of 128-bit granules this permits subordinates to return the data in any order. Complete reordering will be supported by the manager's side.

- Supports MPAM(Memory Partitioning and Monitoring) technology for partitioning and monitoring memory system resources for physical and virtual machines.

- Supports Untranslated transactions and Read data interleaving feature.

- Supports Byte parity check signals for byte parity interface protection.

- Supports all Atomic transactions AtomicStore, AtomicLoad, Atomicswap, and Atomic compare

- Supports 8 different operations like add, clr, eor,set,smax,smin,umax, and umin which can be used with atomicstore and atomic load.

- Support Data checking and Poison signal also which can be used to detect and potentially correct, data bytes which have become corrupted.

- Trace signals are there for debugging, tracing, and performance measurement of systems.

- Support for additional interface signals that enable a slave to indicate the minimum QoS value of transactions that it accepts.

- Support for user Loopback signaling.

- Supports signals that enable access to particular Non-secure memory locations to be controlled

- Supports Wake-up Signaling mechanism

- Support for all type of AMBA AXI5 devices:

- Strong protocol checking Bus Monitor which also provides statistics of the transactions

- Parameterized data and address bus

- Support for all protocol Burst Types, Burst Lengths and Response Types

- Configurable modes for valid and Ready on different channels

- Internal Architecture Based on TLM 2.0

- Rich set of configuration parameters to control AXI5 functionality

- Supports callback in Master and Slave

- AXI5 Verification IP comes with Extensive Coverage Across the Channels

- Supports FIFO, memory and Cache Model integrated

- VIP supports privileged and Secure access

- Supports out of order transaction with Parameterized out of order width

- Supports data interleaving on read data channel

- Supports Endianess check and conversion

- Rich set of error injections

- Supports exclusive transfers

- Dynamic configuration is supported

- Support UVM_RAL Model

- Configurable Memory

- Provides detailed performance monitoring for all the transfers.

- Support GUI analyzer for easy debugging.

- Supports 256 Beat Bursts for INCR.

- Supports interconnect scoreboard for checking data integrity across interconnects.

Deliverables

- AMBA AXI5 Master/Slave Agent

- AMBA AXI5 Bus Monitor and Scoreboard

- AMBA AXI5 Interconnect Scoreboard

- AMBA AXI5 Interconnect Model (Optional)

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Notes