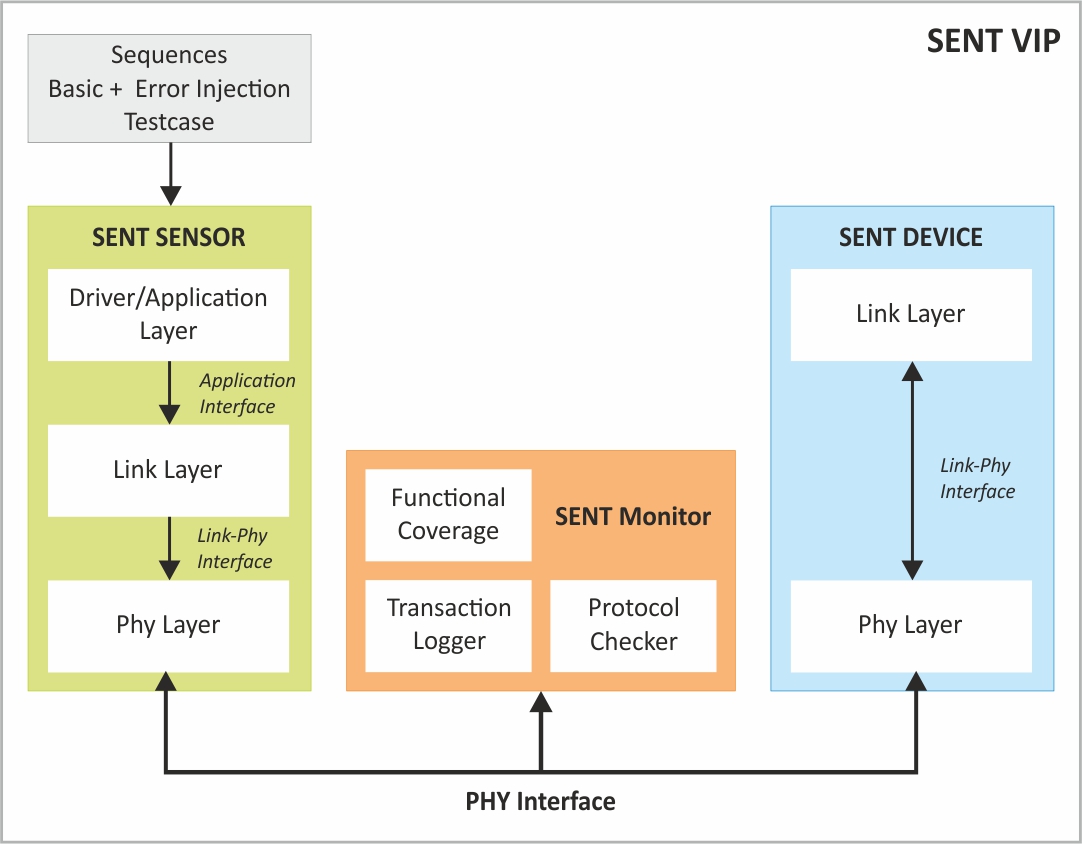

SENT Verification IP

Truechip's SENT Verification IP provides an effective & efficient way to verify the SENT components of an IP or SoC. Truechip's SENT VIP is fully compliant with SENT Specification SAE J2716. The VIP is light weight with easy plug-and-play components so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- Adherent to Single Edge Nibble Transmission (SENT) SAE J2716.

- Supports Both Slow and Fast Channel Transmission

- Supports Following Types of Frames for SLOW channel Transmission

- Short Serial Message Format

- Enhanced Serial Message Format

- Supports Following Types of Frames for Fast Channel Transmission

- Two 12-bit fast channels (6 data nibbles)

- One 12-bit fast channel (3 data nibbles)

- High Speed with one 12-bit fast channel (4 data nibbles)

- Secure Sensor with 12-bit fast channel 1 and secure sensor information on fast channel 2 (6 data nibble)

- Single Sensor with 12-bit fast channel 1 and zero value on fast channel 2 (6 data nibble)

- Two fast channels with 14-bit fast channel 1 and 10-bit fast channel 2 (6 data nibble)

- Two fast channels with 16-bit fast channel 1 and 8-bit fast channel 2 (6 data nibble)

- Supports Enhanced serial message formats with different configurations

- 12-bit data and 8-bit message ID

- 16-bit data and 4-bit message ID

- Supports Configuration of nodes as Sensor, Active or Passive Device.

- Supports programmable clock frequency of operation.

- Supports pause pulse properties

- Minimum length 12 ticks

- Maximum length 768 ticks

- Supports all types of error insertion and detection.

- Checksum errors l Message ID errors

- Oversize errors

- Sync errors

- Supports Glitch insertion and detection.

- Functional coverage for complete SENT features.

- Monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- SENT Verification IP comes with complete test suite to test every feature of SENT specification SAE J2716.

Deliverables

- SENT Sensor/Device/BFM/Agent

- SENT Monitor

- SENT Scoreboard

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes