MIPI CSI2 With D-PHY Verification IP

Truechip's MIPI CSI-2 Verification IP provides an effective & efficient way to verify the components interfacing with MIPI CSI-2 interface of an IP or SoC.

Truechip's MIPI CSI-2 VIP is fully compliant with MIPI Alliance specification for CSI-2 Version 2.1 and MIPI Alliance specification for D-PHY Version 2.1. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- Availability of Conformance and Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Compliant to MIPI CSI-2 Specification version 2.1 and MIPI D-PHY Specification version 2.1 with PPI Interface.

- Support upto 16 virtual channels with D-PHY

- Support for LRTE and data scrambling.

- D-PHY supports MFEN and SFEN for CSI-2 TX and RX respectively for Data Lane Module.

- D-PHY supports MCNN and SCNN for CSI-2 TX and RX respectively for Clock Lane Module.

- Configurable Data Lanes from 1 to 4.

- Supports Data Lane distribution and merging in case of Multi-Lane configuration.

- Supports High Speed, Low Power Escape and Control modes.

- Supports Continuous and Non-Continuous Clock behaviour.

- Supports RAW as well as 8b9b Line Coding.

- Supports Special symbols like EoT, Protocol Marker, Idle 1,Idle2 and Reserved Codes in case of 8b9b Line Coding.

- Supports all Short and Long packet formats.

- Supports ECC and CRC generation as well as correction/detection.

- Supports all primary and secondary CSI-2 Data Formats.

- Supports Frame/ Line Synchronization.

- Supports both Data Type Interleaving and Virtual ChannelInterleaving frames.

- Supports option to configure CSI-2 using CCI commands.

- User can configure MIPI CSI-2 number of lanes, line coding, Continuous Clock behaviour and Low Power Escape as well as ULPS mode using CCI Commands.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using assertions.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in TX and RX.

- Graphical analyser to show transactions for easy debugging.

Deliverables

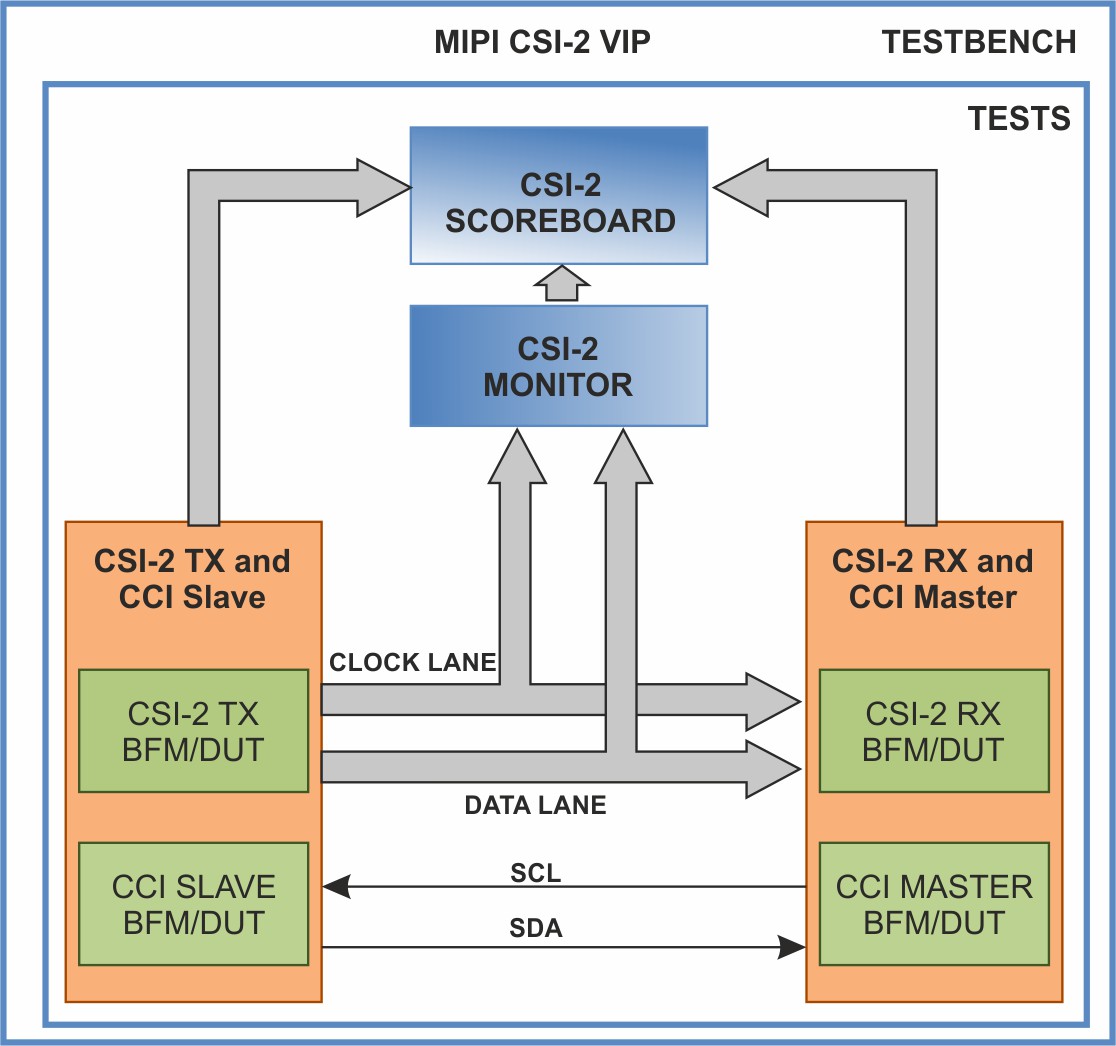

- MIPI CSI-2 TX/RX BFM/Agent

- MIPI CSI-2 Monitor and Score board

- CCI Master/Slave BFM/Agent

- Test Environment & Test Suite :

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Conformance Tests

- Integration Guide, User Manual and Release Notes