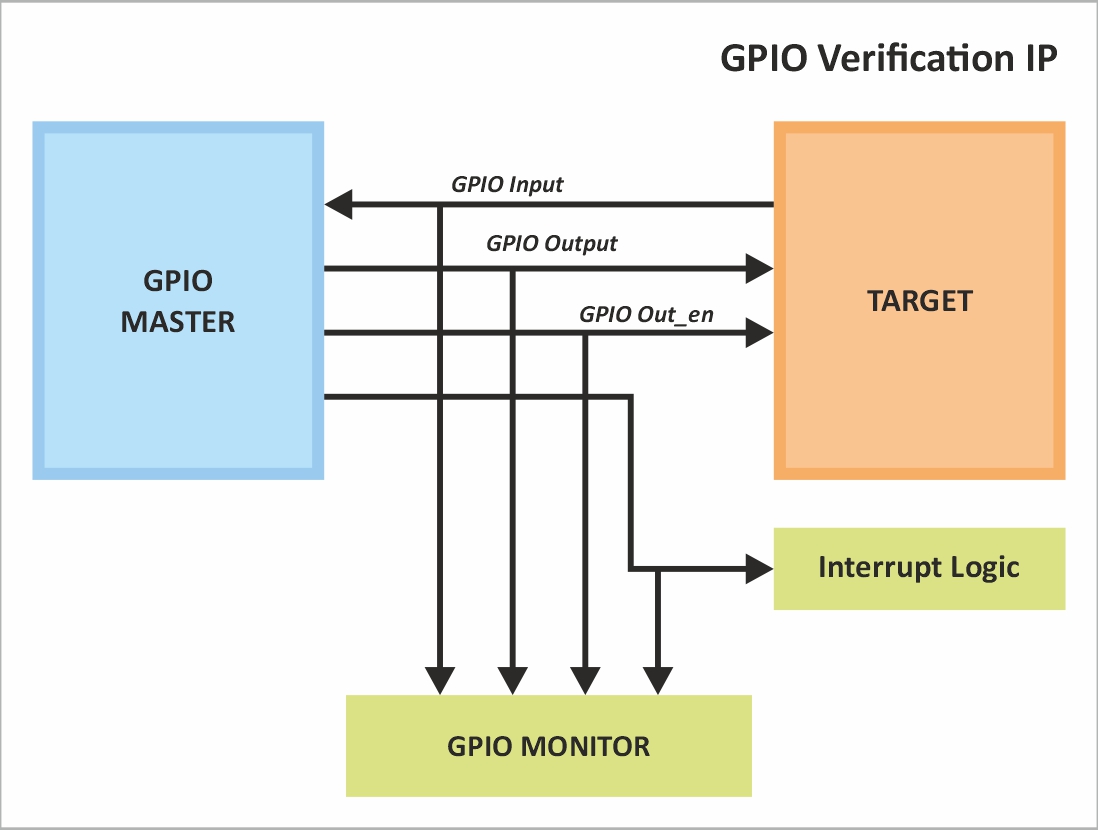

GPIO Verification IP

Truechip’s GPIO Verification IP offers a streamlined and efficient solution for verifying GPIO components within an IP or SoC. Truechip's VIP fully adheres to the GPIO Specification version 2.0 and features a lightweight, plug-and-play design, ensuring that it does not impact the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Each GPIO pin can be individually configured as input, output, or bi-directional.

- Allows receiving data from external sources, sends data to external devices and can act as both input and output based on control signals.

- Verification of GPIO signal levels (e.g., high, low, tri-state)

- Optimized for low latency and high throughput.

- Supports standard GPIO protocols, such as simple input, output, and bi-directional communication.

- Detects signal changes on both rising and falling edges.

- Supports variable bit-width configurations for the number of GPIO pins.

- Configurable sampling frequency to control the timing of reading the GPIO signals.

- Verifies the state of GPIO pins during input, output, and interrupts.

- Supports integration into verification environments like UVM (Universal Verification Methodology).

- VIP can verify wake-up functionality from a low-power mode based on external GPIO signals.

- Allows the introduction of errors such as glitch, stuck-at, and short-circuit conditions to test the robustness of the GPIO logic

- Provides detailed logging of GPIO transactions and state changes for debugging purposes.

- Models interrupt pin behavior with active-high, active low, and edge-triggered configurations.

- Supports testing GPIO-based events like power-on, reset, or system interrupts.

- TheVIPcanscale to verify designs with a large number of GPIO pins, ranging from a few to hundreds of GPIO signals.

- If the GPIO pins are multiplexed with other interfaces like SPI or I2C, the VIP can simulate these conditions.

- Allows verification of designs where multiple GPIO controllers or blocks are present.

Deliverables

- GPIO Tx/Rx/BFM/Agent

- GPIO Monitor

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests and Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes