NoC Verification

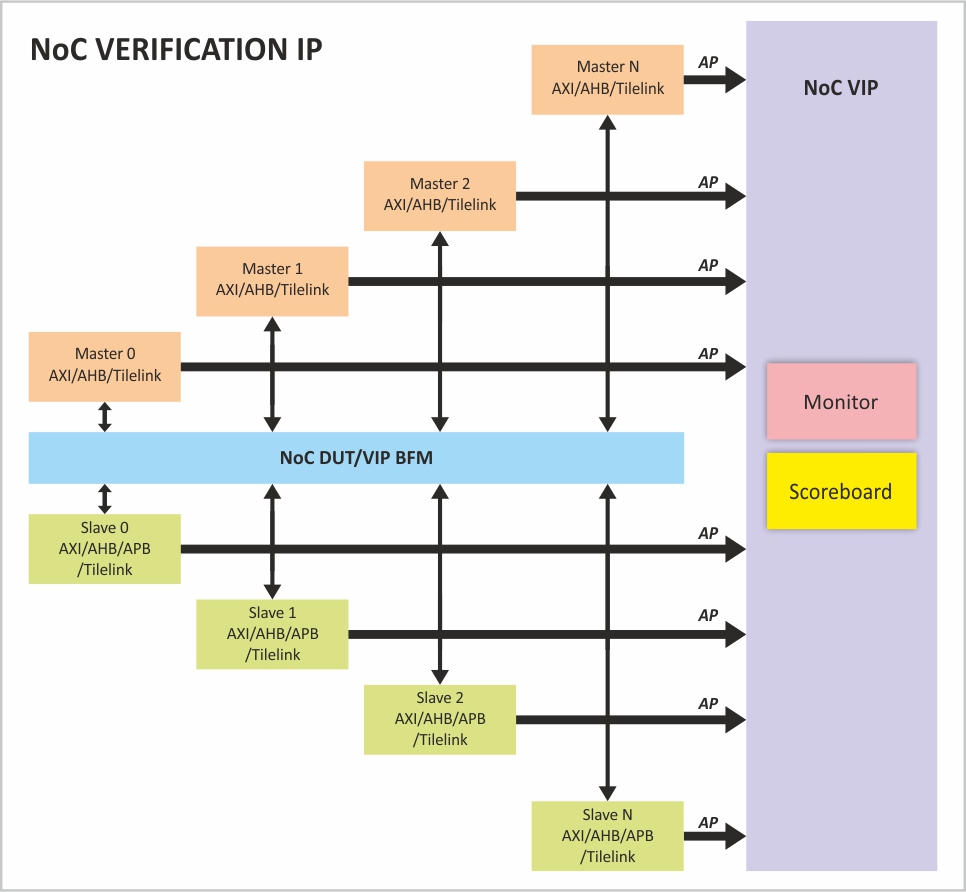

Truechip's NoC Verification IP provides an efficient &

effective way to verify the NoC DUT . It is available in

native Verilog, System Verilog and UVM. Compatible with

Mentor Questa, Cadence NC/ Xcelium and Synopsys VCS

simulator. It can be used in verification of Standalone NOC

IP as well as in SoC environment .

Compliant with latest bus protocols like ARM® AHB3-Lite,5,

ARM® AXI 3,4,4-Lite,5,5-Lite, ARM® APB 2,3,4,5 and SiFive

TileLink Tl-UL, Tl-UH, TL-C with configurable protocols

specified bus width. Users can configure each master and

slave using the register configuration individually. Highly

configurable Slave port address along with security, privilege

and access permission.

Key Benefits

- Available in native SV (UVM/OVM/VMM) & Verilog

- Unique development methodology to ensure highest levels of quality

- 24x5 customer support & response under 90 Min.

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

- Trueye Testbench Generator and analyzer:-

- Automated integration

- Pre IP Verification that Checks integration whether it’s matched with golden metadata configuration or block diagram

- Generated full coverage and configurable Testcases & analyze the full regression.

- Give Fully Automated Report of latency and Bandwidth utilization in the form Graphical analyzer for easy debugging.

- Analyze the performance with respect to different port configuration like peripheral ,DDR ,PCIe ,etc

Features

- Complex network with acyclic agent graph (DAG). Layered and parallel NOC is also supported.

- Any number of master and slave ports is supported. Each port can be configured individually.

- ARM® AHB3-Lite,5, ARM® AXI 3,4,4-Lite,5,5-Lite, ARM® APB 2,3,4,5, SiFive TileLink Tl-UL, Tl-UH, TL-C.

- Configurable memory map for different access types of memory regions.

- Support for different protocols for master and slave port interfaces.

- Each port data width can be different. Apart from the data, other protocols-supported signals can also have different widths.

- Early write response possible.

- Merging and breaking, both possible on transfers.

- Support different phase-shifted frequencies for each Master and Slave.

- Supported Qos throughout Noc

- Support logical and physical conversion of address throughout NOC.

- Both little and big endianness is support.

- Configurable Default slave and Port Priority supported.

- Capable of checking data integrity throughout NOC using NOC Scoreboard.

- Configurable access methods, port security and privilege option Supported.

- Different protocol with different phase shifted clock supported for each port.

- Atomic transaction, NSAID signalling, Read data chunking, Interleaving support, Out of order transfer, Exclusive supports in AXI port.

- Test Environment & Test Suite :

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Compliance Tests

- Provides detailed performance monitoring for all the transfers.

- Supports advanced System Verilog features like constrained random testing.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion

- Graphical analyser to show transactions for easy debugging.

Deliverables

- Monitor, Scoreboard & Matrix

- Master and Slave Port VIP

- AXI, AHB, APB, Tilelink Master, Slave, Monitor & Scoreboard

- Integrated Testbench Example

- TruEye Testbench Generator and analyzer

- Test Environment & Test Suite

- Integration Guide, User Manual, FAQ and Release Notes