ISO/IEC 14443 Verification IP

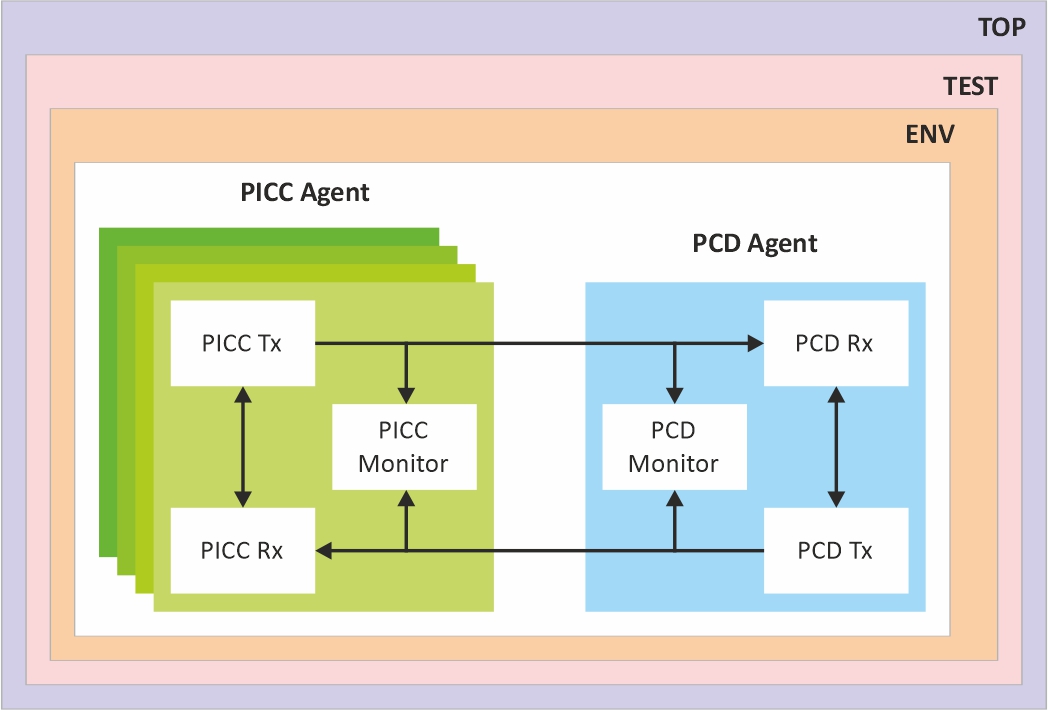

Truechip's ISO/IEC 14443 Verification IP offers a streamlined and efficient solution for verifying System-on-Chip (SoC) and IP designs that incorporate contactless communication. This VIP provides a comprehensive environment for verifying devices acting as either a Proximity Coupling Device (PCD) or a Proximity Integrated Circuit Card (PICC). Fully compliant with the complete ISO/IEC 14443 standard (Parts 1-4), our VIP is a lightweight, plug-and-play solution designed to ensure rigorous verification, minimize design cycle time, and accelerate your time-to-market.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest level of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Fully compliant with ISO/IEC 14443 Parts 1, 2, 3, and 4.

- Complete, configurable functionality for both PCD (reader) and PICC (card) roles.

- Supports both Type A and Type B communication protocols.

- Support for all 6 PICC classes with configurable antenna dimensions

- Supports all standard data rates: 106 kbps, 212 kbps, 424 kbps, and 848 kbps.

- Robust verification of the complete state machine for both Type A and Type B PICCs, including POWER-OFF, IDLE, READY, ACTIVE, and HALT states.

- Comprehensive testing of Type A anticollision using the bit-collision based binary tree search algorithm.

- Full support for Type B anticollision using the slotted Aloha-based method.

- Verifies all initialization commands including REQA, WUPA, REQB, WUPB, ANTICOLLISION, SELECT, and HLTA/HLTB

- Complete support for the T=CL transmission protocol, including protocol activation (RATS, ATS, PPS).

- Verifies all block types:

- I-blocks (Information)

- R-blocks (Receive Ready for ACK/NAK)

- S-blocks (Supervisory for DESELECT and WTX).

- Supports advanced protocol mechanisms including data block Chaining, Multi-Activation, and Waiting Time Extension (WTX).

- Verifies correct block numbering and flow control rules.

- Extensive Error Injection: Provides a rich set of error injection capabilities at both the physical and protocol layers, including:

- CRC and Parity errors

- Invalid command and block formats

- Protocol and state transition violations

- Frame timing errors (FWT, SFGT).

- Comprehensive Monitoring: Monitors, detects, and notifies the testbench of all significant events, including transactions, protocol warnings, timing violations, and errors.

- Randomization: Supports constrained randomization of all protocol fields, timings, and data payloads for comprehensive scenario generation.

- Callbacks: User-configurable callbacks in the driver, receiver, and monitor for customized data processing and testbench interaction.

Deliverables

- ISO-14443 Tx/Rx/ Monitor.

- Testbench Configurations.

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests & Error Scenario Tests

- Assertions & Functional Coverage Tests

- Integration Guide, User Manual and Release Notes