JESD204D Verification IP

Truechip's JESD204D Verification IP provides an effective & efficient way to verify the components (data converters and/or logic devices) connecting with JESD204C link.

Truechip's JESD VIP is fully compliant with standard JESD204D specification from JEDEC standard. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest level of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

Features

- Truechip JESD204D VIP is compliant to the latest JESD204D,C.01,C &B specification by JEDEC

- It is also backward compatible with all the previous versions of JESD204

- Supports a wide range configurations for data converter devices

- Over single and multiple serial links with each link can support single or multiple lanes as per requirements

- Supports serial data rates up to 36 Gbps

- Support physical layer (PHY) classes

- FEC support will be there as per requirement, users can enable and disable

- Multiple FEC Modes are supported with respect to PHY Classes

- One or more convertor devices are supported

- Supports configuration variants:

- Single vs. multiple converters per converter device

- Single lane vs. multiple lanes per converter device

- Single converter device vs. multiple converter devices connected to one logic device

- Supports all working modes:

- Data mode vs. test mode

- Active mode vs. idle mode

- Supports all class devices for B category like B-3, B-6, B-12

- Supports all class devices for C category like, C-S, C-M, C-R

- Supports all Subclasses and ability to support Deterministic latency in Subclass 1:

- Subclass 0 also which is intended for interfacing to JESD204A

- Subclass 1 for RS-FEC link layer (64/66 & 8b/10 also for old compatibility)

- Subclass 2 for 8b/10b link layer(not in 204D for backward compatible)

- Subclass 3 for RS-FEC link layer

- Supports generation of SYSREF or MULTIREF and using them in alignment of LAC(LMFC/LEMC)

- Alignment of LMFC using SYNC~ also supported for device subclass 2

- Supports transport layer mapping as per JESD204C protocol

- Supports oversampling during transport layer mapping

- Supports 64B/80B and 64B/80B link layer with the following Features:

- 64B/66B and 64B/80B encoding

- Sync header stream provides transmission of information parallel to the user data

- Additionally CRC-12 / CRC-3 for error detection, Forward error correction (FEC) for error detection, correction, reporting and command channel for transmitting commands and status information

- Sync header alignment and Extended multiblock alignment at receiver

- 8B/10B link layer is also supported

- Supports both “hard-wired” SYNC interface and “soft” SYNC interface and SYNC interface is compatible with JESD204A & JESD204B

- Supports combined and non-combined SYNC~ signaling for 8B/10B link layer

- Frame and lane alignment and monitoring is supported

- Hard wire and soft sync interface is supported

- Supports up to 32 lanes

- Scrambler can be enabled or disabled

- Supports easy configurations and err-injection scenarios

- Supports functional coverage with bus coverage and configuration coverage

- Supports comprehensive compliance test suite, Constraint random test cases and error injection test cases for verification

- Supports strong protocol monitoring and checks

- Supports transaction logger with the option of GUI

- Supports strict assertion checks.

Deliverables

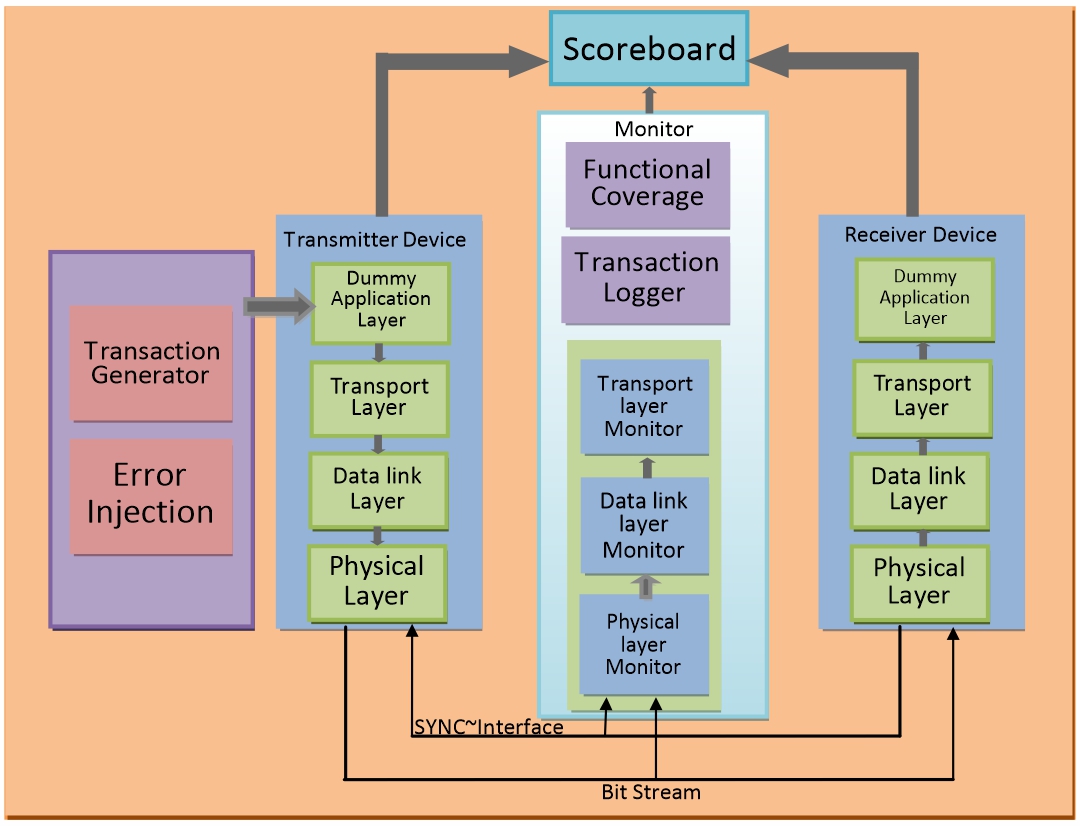

- Transmitter and Receiver Device Agent

- Monitor and Scoreboard agent

- Test environment and test suit

- Basic and directed protocol tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover P Tests

- Integration guide, user manual, release notes, ppt for integration of User’s DUT in VIP environment and integration of VIP in user’s SoC environment