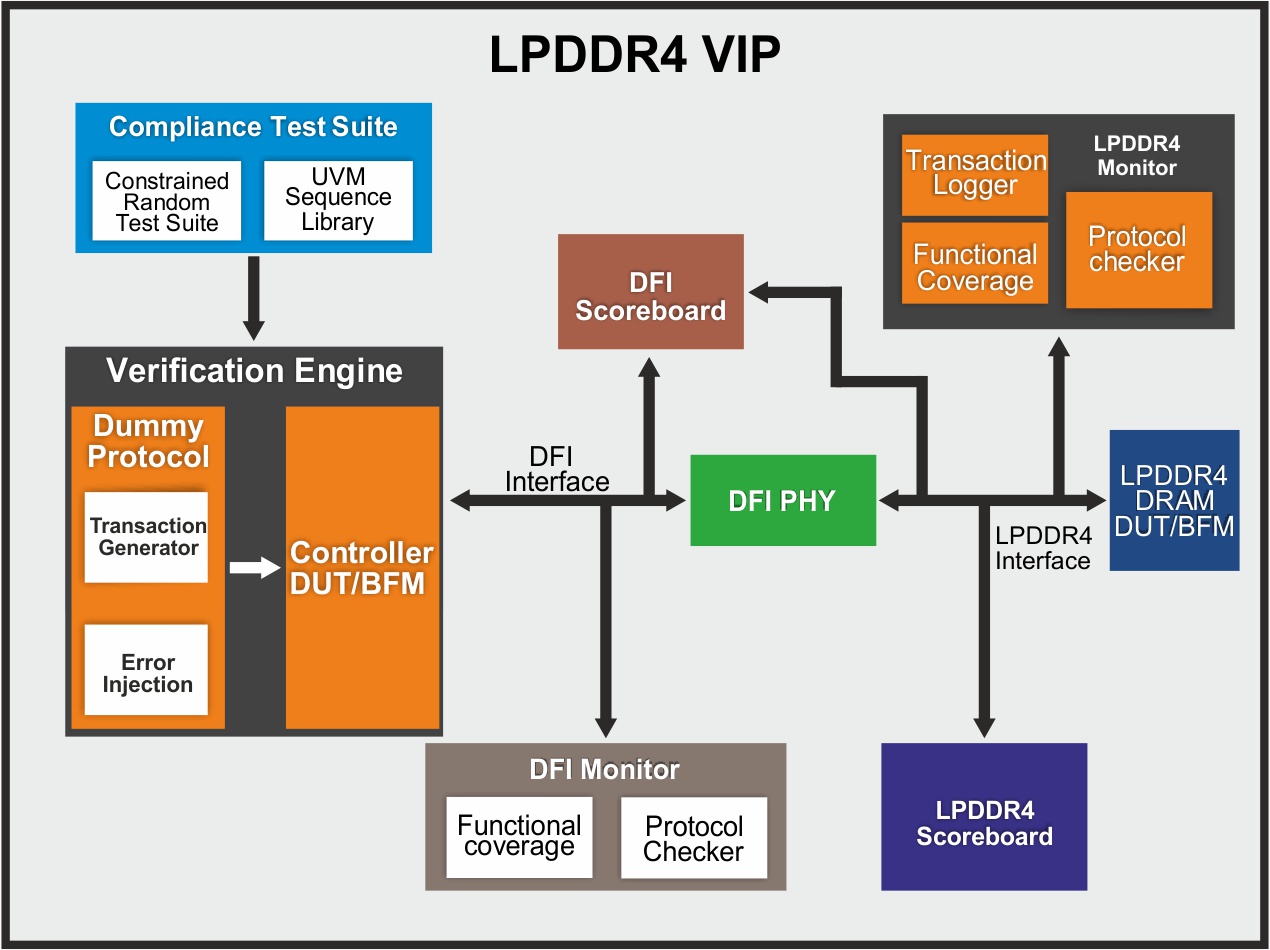

LPDDR4 Verification IP

Truechip's LPDDR4 Verification IP provides an effective & efficient way to verify the components interfacing with LPDDR4 interface of an ASIC/FPGA or SoC.

Truechip's LPDDR4 VIP is fully compliant with Standard LPDDR4 Version JESD209-4B specifications from JEDEC. This VIP is a light weight VIP with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key Benefit

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- Availability of various Regression Test Suites 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Compliant to JEDEC LPDDR4 Specification version JESD209-4B.

- Supports LPDDR4 memory devices from all leading vendors.

- Supports multiple densities: 4Gb to 32Gb.

- Supports capturing of all the valid LPDDR4 commands as per the specs.

- Supports dual channels that can function independently.

- Supports Data Bus Inversion and Data Masking(DM).

- Support for all speed-grades/speed-bins.

- Support for Multiple Ranks architecture.

- Constantly monitors LPDDR4 behavior during simulation.

- Supports Programmable READ/WRITE Latency timings.

- Supports programming of All-Mode Registers.

- Support CA training and DQ calibration.

- Support On-the-fly burst length.

- Support configurable pre-amble and post-amble length.

- Support write data mask and data strobe features.

- Support for Power Down features.

- Supports single-ended mode for clock and strobe.

- Support byte-mode devices from 2 Gb to 32 Gb.

- Support for full-timing as well as behavioral versions in one model.

- Support for all timing delay ranges in one model: min and max.

- Reports various timing errors, which can be used to check any timing violations.

- It provides full control to the user to enable/disable various types of messages.

- Supports advanced SystemVerilog features like constrained random testing.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real-time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built-in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Monitor, Controller, and Memory Model BFMs.

- Graphical analyzer to show transactions for easy debugging.

Deliverables

- LPDDR4-SDRAM Model

- LPDDR4 Monitor and Scoreboard

- LPDDR4 Memory Controller BFM/Agent

- LPDDR4 PHY BFM model

- LPDDR4 Phy Monitor and Scoreboard

- Test-Bench Configurations

- Test Suite (Available in Source code) :

- Basic Protocol Tests

- Directed & Random Tests

- Assertion and Cover Point Tests

- Integration Guide, User Manual, and Release Notes

GUI analyzer to view simulation packet Flow