LPDDR5/5X Verification IP

Truechip's LPDDR5/5X Verification IP provides an effective & efficient way to verify the LPDDR5X components of an IP or SoC. Truechip's LPDDR5/5X VIP is fully compliant with LPDDR5/5X Specification JESD209-5C .

The VIP is lightweight with easy plug-and-play components so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- Compliant to JEDEC LPDDR5/5X specification.

- Supports LPDDR5/5X memory with all compliant vendors.

- Supports all LPDDR5/5X density upto 32 GB.

- Supports x16 and x8 DQ signals

- Supports LPDDR5/5X 4Banks and 4Bank group , 16 Banks modes

- Supports MR8 to switch between LPDDR5/5X SDRAM.

- Supports all LPDDR5 speed-grades/speed-bins and LPDDR5X 7500 and 8533 Data rate as well.

- Supports RX offset calibration training for LPDDR5X SDRAMs.

- Supports all LPDDR5/5X mode registers.

- Supports Direct refresh managements.

- Supports capturing of all the valid LPDDR5/5X commands as per the specs.

- Supports Data Bus Inversion and Data Masking (DM).

- Constantly monitors LPDDR5/5X behaviour during simulation.

- Supports Programmable READ/WRITE Latency timings.

- Support all LPDDR5/5X trainings.

- Support for Power Down features.

- Support for all timing delay ranges in one model: min and max.

- Error injection is available for extensive failure testing

- Extensively detailed simulation & debug logs.

- Error ID mechanism to show spec section in description of the obtained error.

- Supports Constraint Randomization.

- Callbacks in host, device for user processing of data.

- Complete test-suit to verify each feature of LPDDR5/5X standard.

- Built in Coverage Analysis.

- Graphical Analyser for easy debugging.

- Transaction logger that prints all the logging information.

- Functional coverage for complete LPDDR5/5X features.

- Monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- LPDDR5/5X Verification IP comes with complete test suite to test every feature of LPDDR5/5X JESD209-5C

Deliverables

- LPDDR5/5X SDRAM Model

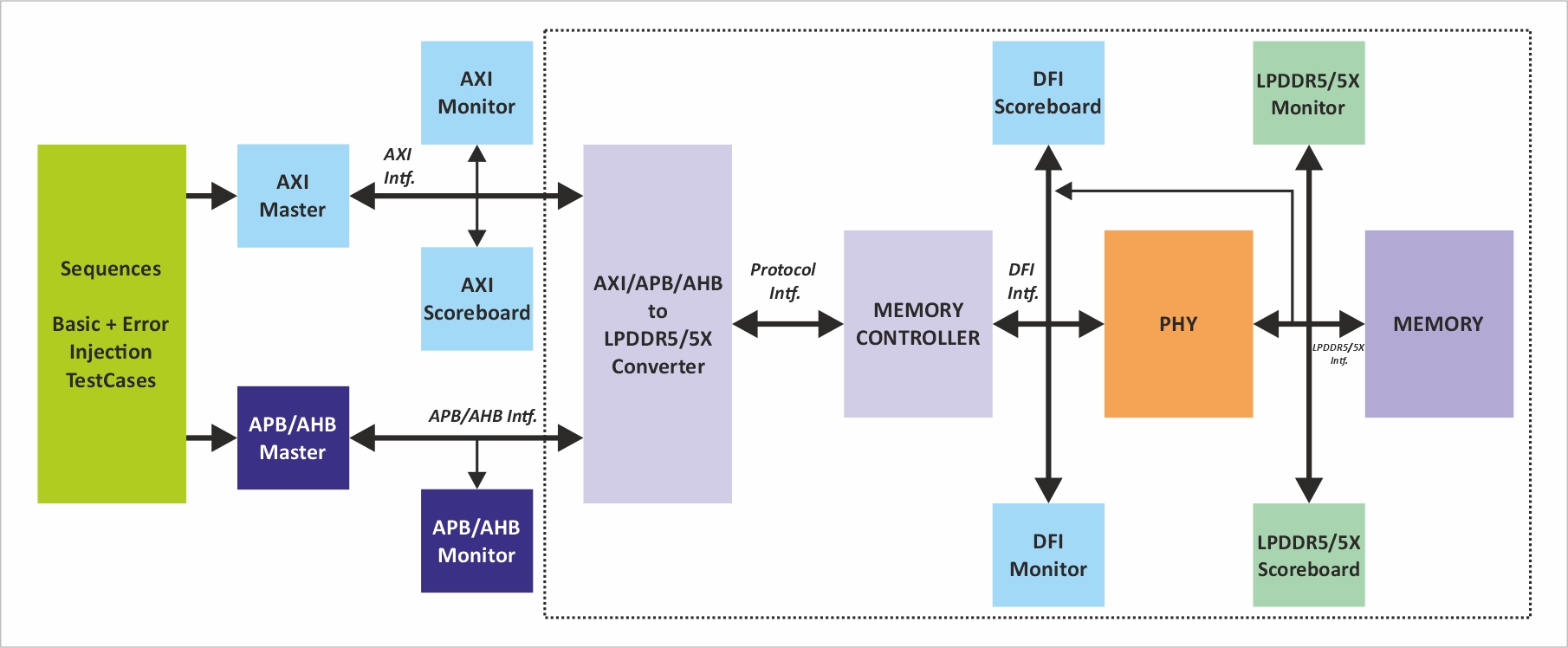

- LPDDR5/5X Functional memory controller BFM/Agent

- LPDDR5/5X Monitors and Scoreboard

- LPDDR5/5X PHY BFM Model

- LPDDR5/5X DFI monitor and scoreboard

- Test-Bench Configurations

- Test Suite (Available in Source code)

- Basic Directed Tests

- Random Tests

- Error Injection Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes