PMBus 1.5 Verification IP

Truechip's PMBus Verification IP provides an effective and efficient way to verify the components interfacing with PMBus interface of an IP and SOC. Truechip's PMBus VIP is fully compliant to PMBus Specification version 1.5. The VIP is light weight with easy plug-and- play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest level of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Fully compliant with Rev. 1.5 of the PMBus Specification.

- Support for all SMBus protocols with and without PEC (Packet Error Checking).

- Support for SMBus ARP (Address Resolution Protocol) for dynamically assigning a unique address to each slave device.

- Support Group command protocol for multiple PMBus device communication.

- In addition to command code protocols also supports extended command code protocol.

- Supports ZONE_CONFIG & ZONE_ACTIVE commands.

- Support Zone read and Zone write to access some or all devices on bus including their pages.

- Support for Command control code and all PMBus commands.

- Support STATUS_BYTE And STATUS_WORD command for fault management and reporting

- Support for security commands including ACCESS_CONTROL, P ASSKEY, SECURITY_BYTE, SECURITY_BLOCK and SECURITY_AUTOINCREMENT.

- Supports primary memory and buffer memory for security commands.

- Supports deterministic random bit generator for read nonce.

- Supports generation of transactions with UVM register model.

- Built in Bus Monitor provides extensive protocol checking.

- Supports various error injection and detection.

- Provides verification scalability using functional coverage.

- Provides logging facility for bus traffic in the ASCII format and in user configurable mode.

- Supports timing checks in the Monitor.

- Callbacks for user-defined transfers.

- Supports transaction logging with detailed description of each transfer

- Graphical analyser to show transactions for easy debugging.

Deliverables

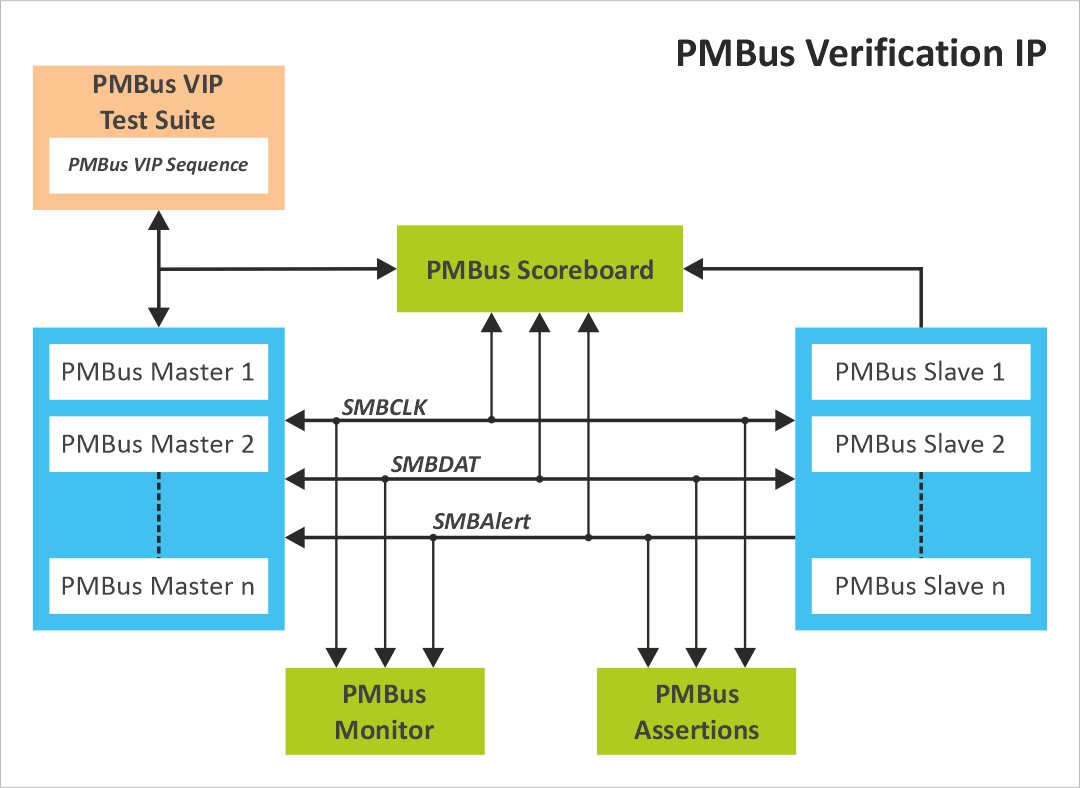

- PMBus Controller/Target BFM/Agent.

- PMBus Monitor and Scoreboard

- Testbench Configurations.

- Test environment and test suite

- Basic and directed protocol tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes