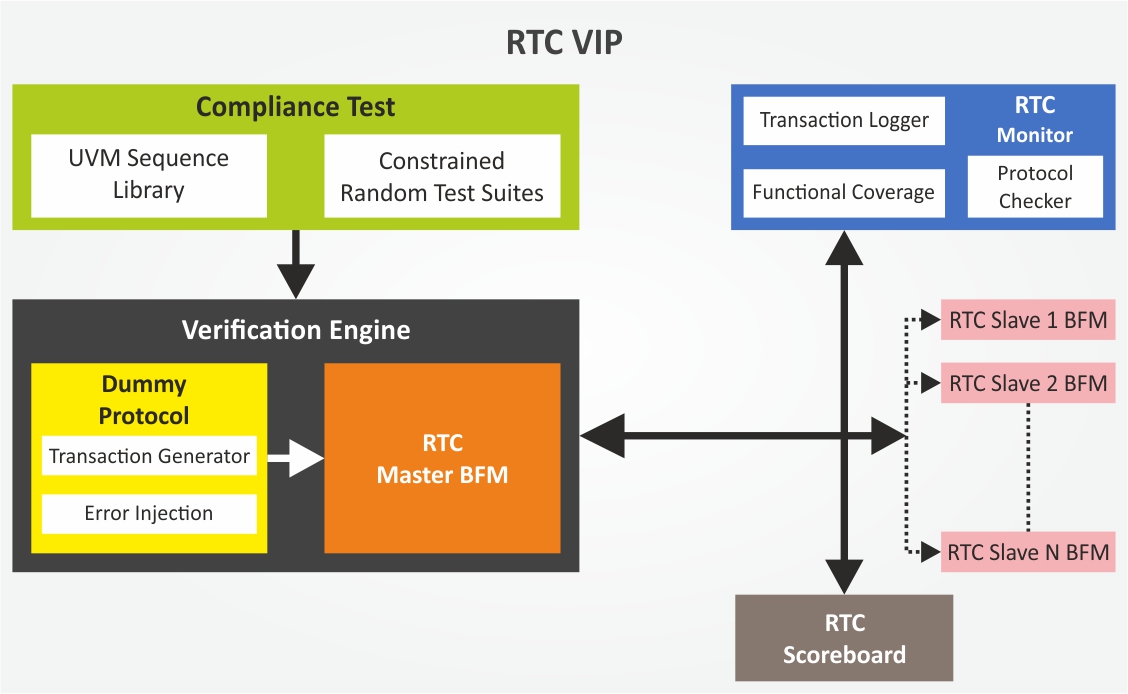

RTC Verification IP

Truechip's RTC verification IP provides an effective and efficient way to verify the components (data converters and/or logic devices) connecting with RTC link. Truechip's RTC VIP is fully compliant with SPI Specification 512Mbit(64Mbyte) 3.0V SPI FLASH MEMORY S25FL5122, DS3234 maxim_spi_rtc and JEDEC JESD251A expanded serial peripheral interface specification with the help of JEDE JESD216D-01 SFDP specification. This VIP is lightweight VIP with easy plug -and -play interface so that there is no hit on the design time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure highest levels of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support.

- Unique and customizable licensing models.

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs.

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Compliant to SPI Specification 512Mbit(64Mbyte) 3.0V SPI FLASH MEMORY S25FL5122

- Compliant to JEDEC JESD251A expanded serial peripheral interface specification with the help of JEDEC JESD216D-01 SFDP specification.

- Follows RTC basic specification as defined in DS3234 maxim_spi_rtc.

- Supports connection to any SPI Memory and SPI Master IP communicating with a CYPRESS spi flash memory model.

- Supports configurable timing parameters and multi slave configurations.

- Supports multi slave memory.

- Supports Master and Slave Mode.

- Supports data width of 8 bits.

- Supports baud rate selection.

- Supports internal clock division checks.

- Supports single and burst transfer mode

- Supports on the fly generation of data.

- Provides full control to the user to enable / disable various types of messages.

- Integrates easily in any verification environment.

- Supports full timing models or bus functional models.

- Supports advanced System Verilog features like constrained random testing.

- Supports Callback/ User Configuration in all components.

- Supports ECC.

- Support Mode 0 (CPOL=0) and Mode 3 (CPOL=1)

- Supports SDR, DDR, DUAL, DUAL I/O, DDRDUAL I/O, QUAD, QUAD I/O ,DDRQUAD I/O modes.

- Supports all the commands mentioned in the CYPRESS spi specification.

- Has assertion and coverage with more than 95% functional coverage.

- Has constraint random testcases to assure the specification is thoroughly met.

- Supports all possible frequencies mentioned in the specification.

- Supports optional data masking feature.

- Supports 1s-1s-1s and 8D-8D-8D mode and dynamic mode between them

- Supports a wide variety of Dynamic as well as Static Error Injection scenarios

Deliverables

- SPI slave flash memory Model

- SPI Monitor & Scoreboard

- SPI MASTER BFM/Agent

- Test-Bench Configurations

- Test Suite (Available in Source code)

- Basic Protocol Tests

- Directed & Random Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes