SD Card Verification IP

Truechip’s SD Card Verification IP provides an effective & efficient way to verify the components interfacing with SD Interface of an ASIC/FPGA or SoC.

Truechip’s SD Card VIP is fully compliant with Standard SD card v7.00 specifications from SD Organization. The VIP is a light weight VIP with easy plug-and-play interface so that there is not hit on the design time and simulation time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and verilog

- Unique development methodology to ensure highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across the VIP

- Provide complete solution and easy integration in IP and SoC environment

Features

- Compatible with all the versions V1.0, 2.0, 3.0, 4.0, 5.0, 6.0, 6.10, 7.00

- Supports all Capacity of Memory i.e.

- Standard Capacity SD Memory Card (SDSC)

- High Capacity SD Memory Card (SDHC)

- Extended Capacity SD Memory Card (SDXC)

- Ultra Capacity SD Memory Card (SDUC)

- Supports all Voltage range:

- High Voltage SD Memory Card – Operating voltage range : 2.7-3.6V

- SD Express Memory Card – Operating voltage range VDD1: 2.7-3.6V, 1.70-1.95V optional VDD3: 1.14-1.30

- Supports Card detection for both SD mode and SPI mode

- Supports all UHS-1/2 mode

- Supports all Bus Speed Mode – Using 4 parallel data lines

- Default Speed mode : 3.3V signaling, Frequency up to 25 MHz, up to 12.5 MB/sec

- High Speed mode : 3.3V signaling, Frequency up to 50 MHz, up to 25 MB/sec

- SDR 12 : UHS-1 1.8V signaling, Frequency up to 25 MHz, up to 12.5 MB/sec

- SDR 25 : UHS-1 1.8V signaling, Frequency up to 50 MHz, up to 25 MB/sec

- SDR 50 : UHS-1 1.8V signaling, Frequency up to 100 MHz, up to 50 MB/sec

- SDR 104 : UHS-1 1.8V signaling, Frequency up to 208 MHz, up to 104 MB/sec

- DDR 50 : UHS-1 1.8V signaling, Frequency up to 50 MHz, sampled on both clock edges, up to 50 MB/sec

- Switch function command supports Bus Speed Mode, Command system, Drive strength, and future functions

- Supports Command Queue and cache for performance

- Supports Correction of memory field errors

- Supports Card removal during read operation will never harm the content

- Supports Content protection mechanism – Complies with highest security of SDMI standard

- Supports Password protection of cards (CMD42- LOCK_UNLOCK)

- Supports Write Protect feature using mechanical switch

- Supports Built-in write protection features (permanent and temporary)

- Supports Card Detection (Insertion/Removal)

- Support for Application specific commands

- Supports Comfortable erase mechanism

- Provides full control to user to enable/disable various types of messages

- Supports full timing models or bus functional models

- Supports Dynamic as well as static Error injection scenarios

- On the fly protocol checking using protocol check function, static and dynamic assertions

- Provides a comprehensive user API (callbacks) in BFMs

- Supports advanced System Verilog features like constrained random testing

- Built in Coverage analysis.

- Graphical Analyzer to show transactions for easy debugging.

Deliverables

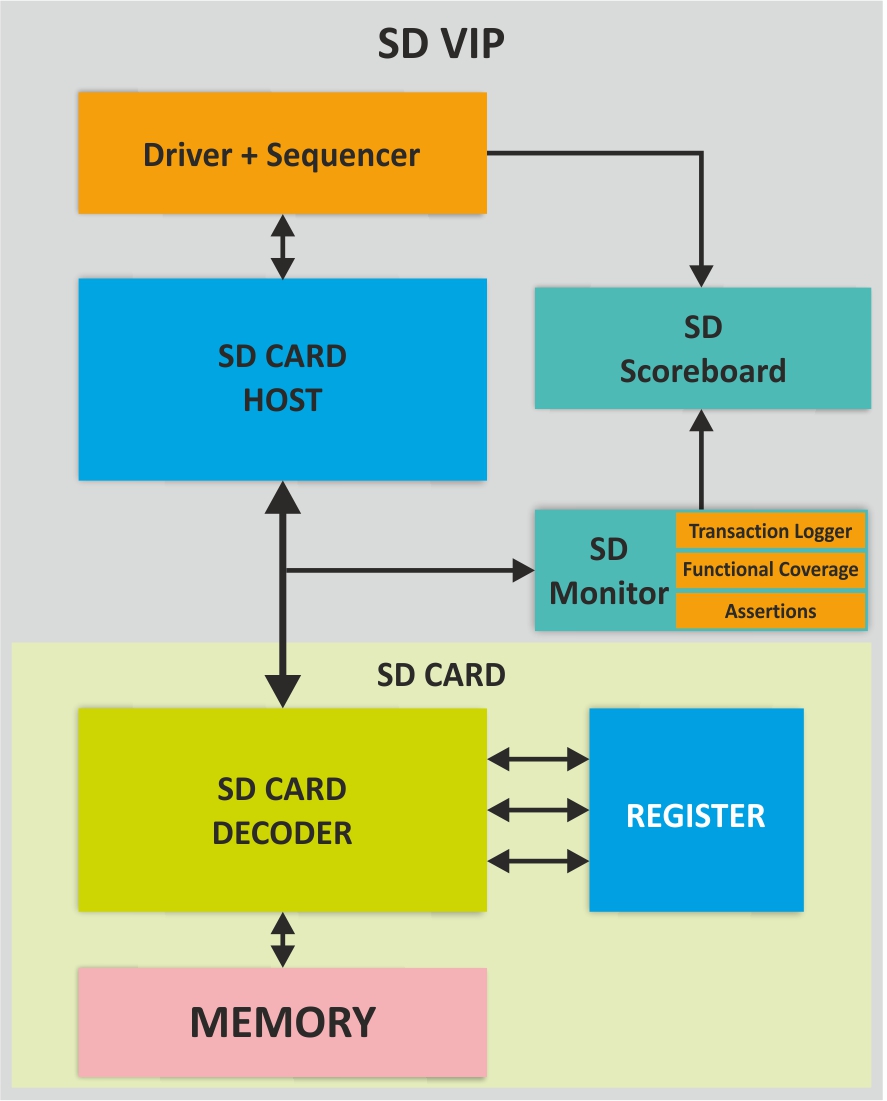

- SD Memory Card Model

- SD Monitor & Scoreboard

- SD Host Model

- Test-Bench Configurations

- Test Suite (Available in Source code)

- Basic Protocol Tests

- Directed & Random Tests

- Assertions & Cover Point Tests

- Error injection Scenarios Tests

- Integration Guide, User Manual and Release Notes

- GUI analyzer to view simulation packet flow.

- Integrated solution for SD Express with SD card, PCIe and NVMe