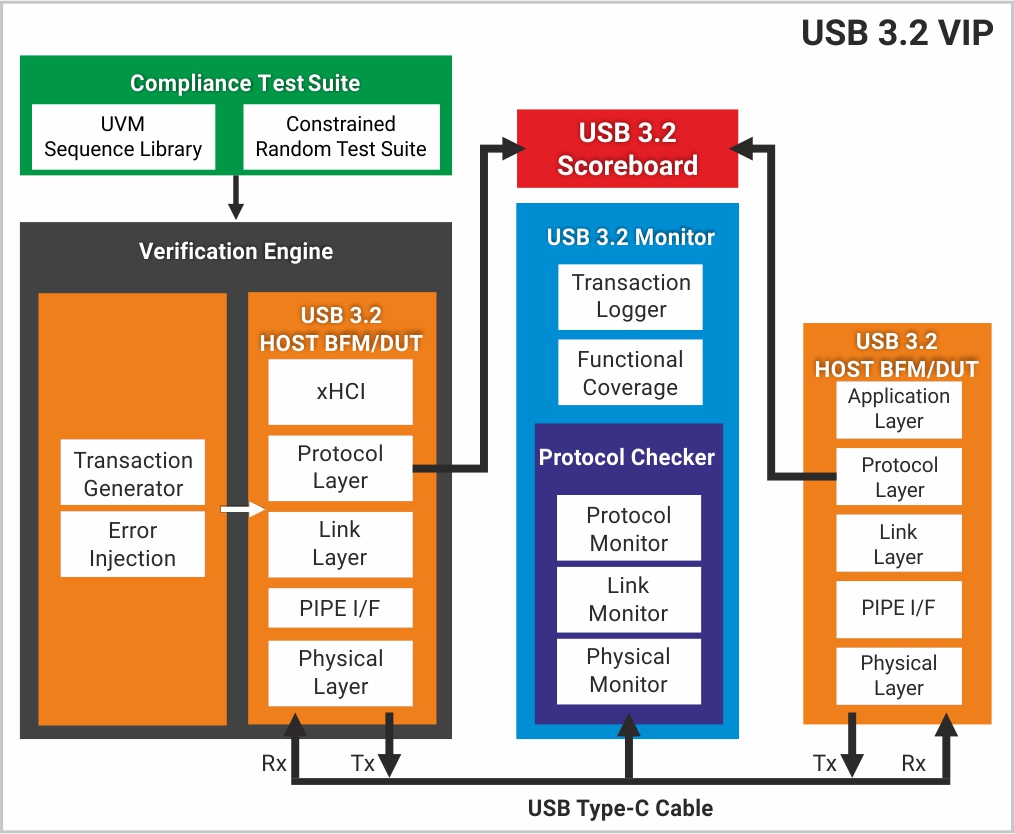

USB 3.2 Verification IP

Truechip's USB3.2 Verification IP provides an effective & efficient way to verify the components connected with USB3.2 interface of an IP or SoC. Truechip's USB3.2 VIP is fully compliant with standard USB3.2 Specification version 1.1 from USB-IF. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Fully compliant with USB 3.2 specification version 1.1, xHCI Specification Revision 1.2, and Pipe Interface 6.1.1 with Message Bus Interface for USB3.2 Architecture with backward compatibility to USB3.1, USB3.0 and USB2.0 (including USB2.0, USB 3.0. OTG)

- Supports USB Type-C.

- Supports up to 128 devices including hub and device on any tier level.

- Supports 15 IN and 15 OUT and 1 control endpoint for each device.

- Supports all transfer types; Control, Bulk, Bulk Stream, Interrupt with flow control and retry mechanism.

- Support for pipelined isochronous and Smart Isochronous transfer.

- Supports configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints.

- Supports out of band active stream list exchange, HIMD and Stream Proposal rejection feature.

- Supports bursting in all transfer modes (Up to Max Burst size).

- SuperSpeedPlus supports Precision Time Measurement (PTM) (LDM protocol).

- Enhanced traffic and flow control management in link layer.

- Supports both Type 1 And Type 2 Traffic Classes.

- Different Header packet framing for Deferred and Non-Deferred DPH.

- Supports all compliance patterns - CP0 to CP8 over Gen1 Rate and CP9 to CP16 over Gen2 Rate for Compliance Mode LTSSM state.

- Support for all power management states (U1, U2, U3) with U1 Inactivity, U2 Inactivity timers.

- Support for generation of all link commands defined in the USB3.2 Specification

- Dual lane support (Gen2x2 and Gen1x2) with Skew and De-Skew capabilities with SSC/PPM support.

- Configurable PIPE Interface width – 8b,16b or 32b.

- User controlled device attach/ detach function.

- Supports UAS (USB Attached SCSI) and BOT (Bulk-Out Transfer)

- Configurability to enable required data rate (8b/10b or 128b/132b) & Speed negotiation (x1 or x2)

- Comprehensive Compliance Test Suite for Physical, Link and Protocol Layer, xHCI Verification.

- Call backs support in all Layers to provide user-controlled error injection.

- Automated masking of all types of error injections.

- Complete on-the-fly Static and Dynamic Assertion Protocol Checks

- Built-in Functional coverage analysis

Deliverables

- USB3.2 Host/Device

- USB3.2 BFM/Agents for:

- Physical Layer

- Link Layer

- Protocol Layer

- Application Layer

- xHCI VIP compatible with xHCI Specification Revision 1.2

- USB3.2 Layered Monitor and Scoreboard

- USB3.2 Test Environment and Test Suites:

- Basic and Directed Protocol Tests

- Low Power Tests

- Error Injection Tests

- Compliance Test Suite (CTS)

- Stress Tests for each Standard layer

- Random Tests

- Assertions and Cover Points

- Integration Guide, User Manual, Quick Start Guide, Testplan, Regression Lists and Release Notes.

- TrueEye GUI analyzer for simulation packet flow and usage guide