loading...

Generic method for using a dynamic class based environment inside a static top level environment using wrappers.

With the advent of Hardware Verification Languages (HVLs) like SystemVerilog (SV), the memory footprint Verification IPs (VIPs) is generally smaller than older VIPs, which were based on Verilog or VHDL. This is primarily because, SV based VIPs may have objects created dynamically (i.e. in between the simulation) and also objects get freed when not needed thus freeing up memory. Whereas in case of older VIPs based on Verilog or VHDL, the instances or variables never free the memory as they are static in nature and they consume memory from the start of simulation till the end.

Any System on Chip (SoC), today will typically have over a hundred IPs instantiated. Hence it requires many “Verification IPs” (VIPs) to be instantiated in the testbench, for verification. Since SoCs are already large in size and complexity, having lighter weight VIPs results in lesser memory and faster simulation, this eases the task of SoC verification. However, a lot of companies still have legacy test environments created. In such a case, migrating from an existing SoC test environment to a fully HVL based test environment is time consuming and the project schedules do not permit such additional time. So generally people tend to sacrifice the advantages of SV based VIPs and to stick to the older/ legacy VIPs, that have static memory and are bulky.

In this article, our team has proposed a methodology in which we have kept both the aspects in mind. We are proposing a methodology that helps to create a Verilog type user interface for a HVL or SV based Verification IP. Such a VIP can be instantiated in the legacy and static test environment of the SoC and the VIP still provides the advantages of lower memory footprint.

The risks are many:

The only solution for such an issue is merging both the problems, and coming out with a unique answer that gives a familiar interface with dynamic capabilities!

In general every company follows some methodologies for creating their VIP environments

Some of the standard methodologies are:

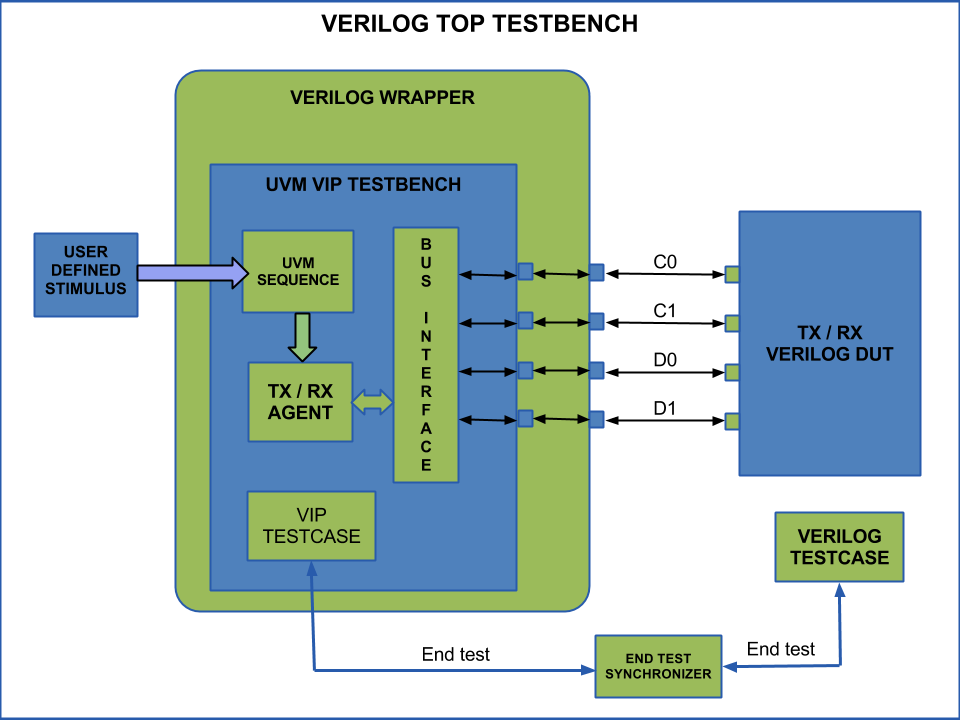

One such solution is to wrap the SV or UVM based VIP in a Verilog wrapper, thug giving it the look and feel as required by the legacy SoC test environment and allowing the dynamic features of HVL to function internally. Let us talk in detail about the UVM to Verilog environment converter (Wrapper):

There were many challenges at first when this task was taken up. Following a general Idea that a familiar interface should be our first priority we targeted the boundaries of the VIP .

CONCLUSION:

In this way, we can get the advantages of HVL based Verification IPs even in static test environments. The important points to be taken care are interface for instantiation, phasing of HVL VIP and the static environment, and the testcase finish logic to be synchronized between the HVL and static environments.