loading...

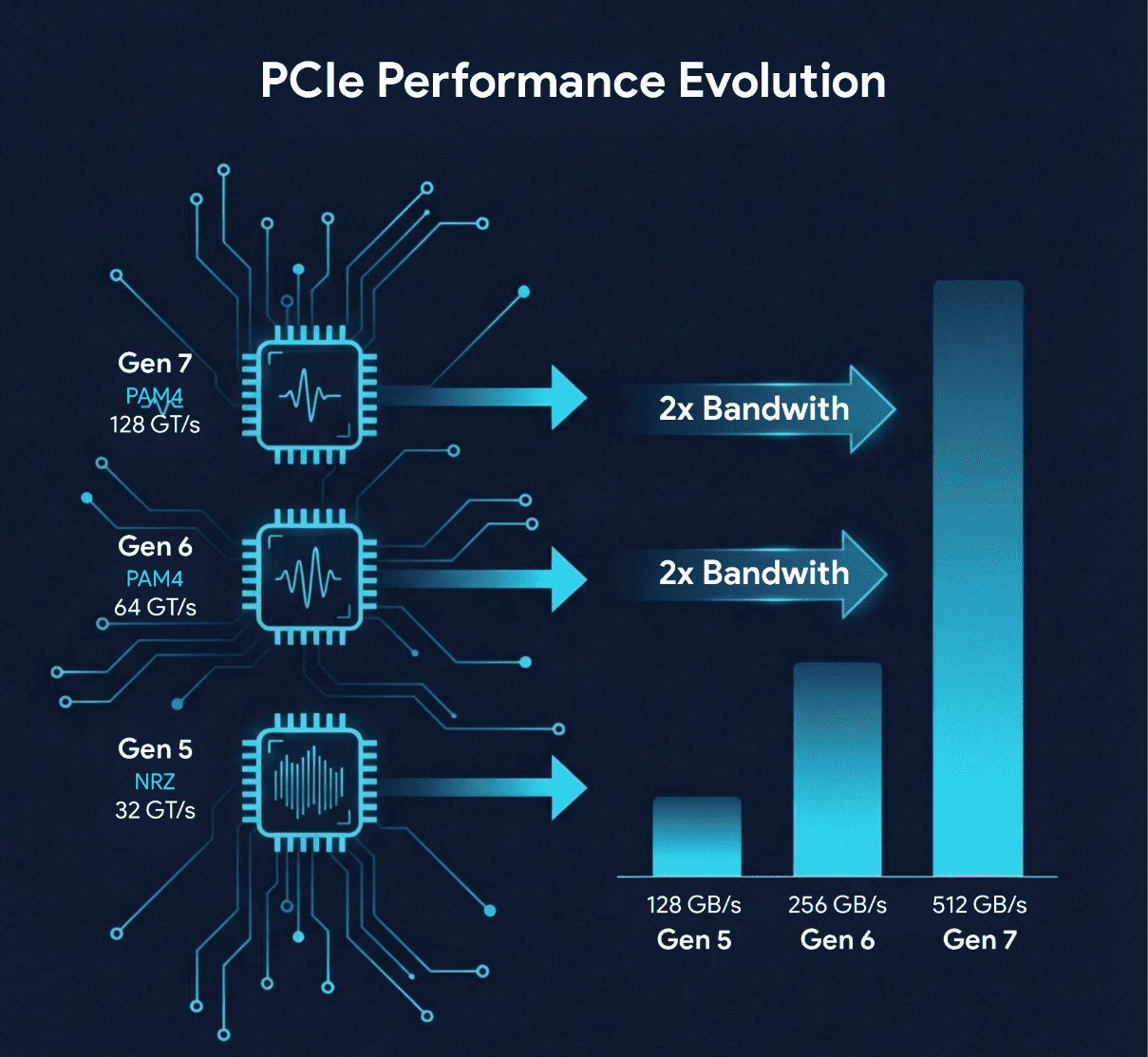

The PCI Express (PCIe) Gen 7 specification is a major evolution for data-centric applications, offering a groundbreaking data rate of 128.0 GT/s per lane—double that of Gen 6. This performance leap is achieved by leveraging PAM4 signaling and Flit Mode for high bandwidth, low latency, and efficient power use. Given the complexity of this new standard, robust verification solutions, such as Truechip's PCIe Gen 7 Verification IP (VIP), are critical for validating controllers and rapidly accelerating time-to-market.

.png)

PCIe Gen 7 scales up to 128 GT/s per lane, which, with 16 lanes (x16 configuration), delivers an astonishing ~512 GB/s of bidirectional bandwidth, a 2× improvement over Gen 6 and 4× over Gen 5.

|

PCIe Generation |

Signaling |

Data Rate (GT/s) |

x16 Throughput (GB/s, bidirectional) |

|

Gen 5 |

NRZ |

32.0 |

128 |

|

Gen 6 |

PAM4 |

64.0 |

256 |

|

Gen 7 |

PAM4 |

128.0 |

512 |

(Source: PCI-SIG)

The increased data rate demands sophisticated equalisation and retimer strategies, new encoding mechanisms, and stringent signal integrity requirements.

PCIe Gen 7 continues the use of PAM4 (4-level Pulse Amplitude Modulation) signaling introduced in Gen 6, but extends it to 128 GT/s, achieving 2 bits per UI (Unit Interval).

Because PAM4 levels are closer together, Gen 7 implements improved Equalisation Training Sequences (TS1/TS2) and adaptive Receiver/Transmitter equalisation, essential to compensate for inter-symbol interference and channel loss.

Flit Mode (Flow Control Unit Mode), introduced in PCIe Gen 6, is mandatory in Gen 7 and defines fixed-size packets (256 bytes) for deterministic latency and simplified error recovery.

Within each flit:

At 128 GT/s, signal degradation and channel loss are major challenges. PCIe Gen 7 introduces:

These innovations ensure Gen 7 maintains PCIe’s hallmark backward compatibility while addressing next-generation signal integrity demands.

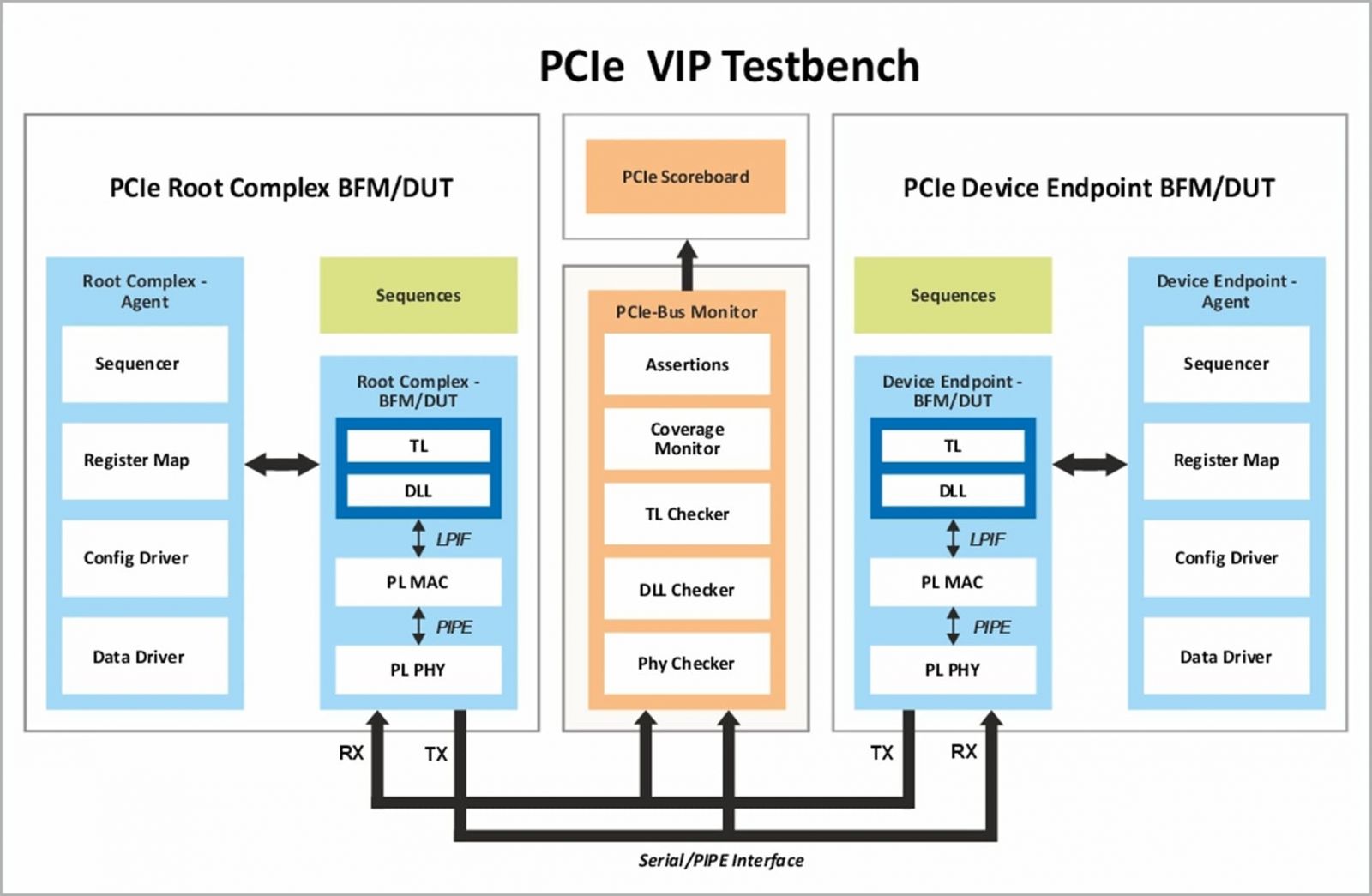

As speed and complexity rise, verifying a PCIe Gen 7 controller requires:

Traditional verification methodologies are no longer sufficient — they need automation, flexibility, and high-speed simulation capabilities.

Truechip, a PCI-SIG member and long-time provider of leading VIP solutions, offers a comprehensive PCIe Gen 7 VIP suite that is fully aligned with the 7.0 specification.

🔗 Truechip PCIe Gen 7 VIP Overview

PCIe Gen 7 marks a significant step toward terabit-class connectivity, setting the foundation for AI, HPC, and data-center architectures that rely on ultrafast, reliable interconnects. With features such as PAM4 signaling, 128 GT/s data rates, Flit Mode with ECC, and optical retimers, it defines the future of low-latency and high-bandwidth communication.

However, as the specification evolves, verification complexity grows exponentially. Truechip’s PCIe Gen 7 VIP stands as a robust, scalable, and fully compliant environment that empowers design teams to validate Gen 7 controllers faster and with higher confidence — from early simulation to compliance-ready silicon.