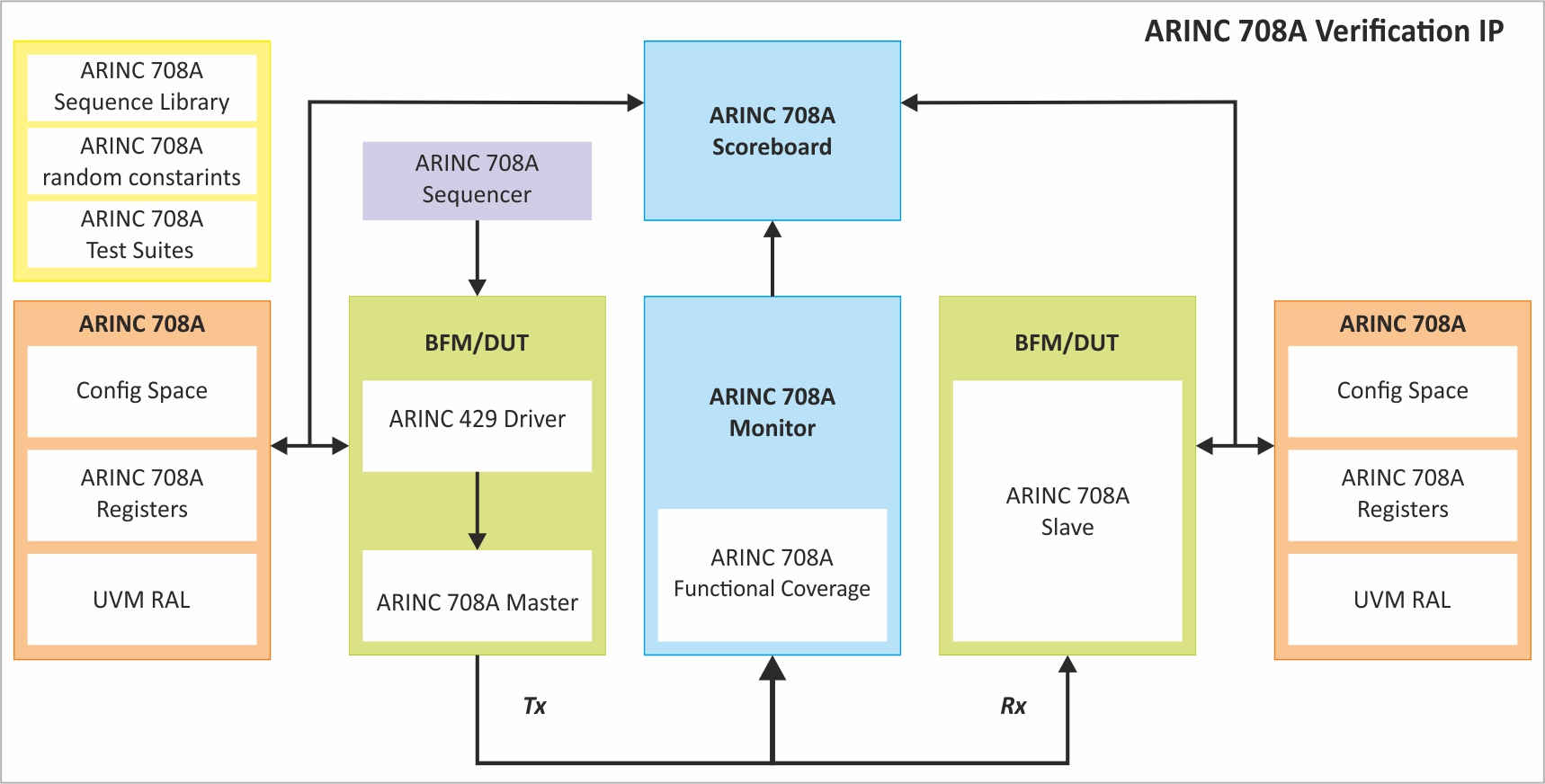

ARINC 708A Verification IP

Truechip's ARINC 708A Verification IP provides an effective & efficient way to verify the Avionics components of an IP or SoC. Truechip's VIP is fully compliant with ARINC 708A Specification version 1.0. The VIP is lightweight with easy plug-and-play components so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- Available in Verilog, System Verilog, and UVM.

- Control Word information can be user-configurable / Random. (Protected By parity).

- Data word header will be according to the 270 271 label Frame received from Control Word.

- Support for Hazards, Faults, and Errors.

- Error response types supported.

- Supports different memory update Mode Configurations.

- Supports a wide variety of error injection scenarios.

- Supports continuous or non-continuous transactions.

- Callbacks in Master for various events.

- Control Word is transmitted using ARINC 429 Protocol while Data Word using ARINC 708 / 708A.

- Control Words Support 270, 271 Labels Frame Format.

- Data Words Supports Label 055 Octal

Deliverables

- ARINC 708A Tx/Rx/BFM/Agent

- ARINC 708A Monitor

- ARINC 708A Scoreboard

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Notes