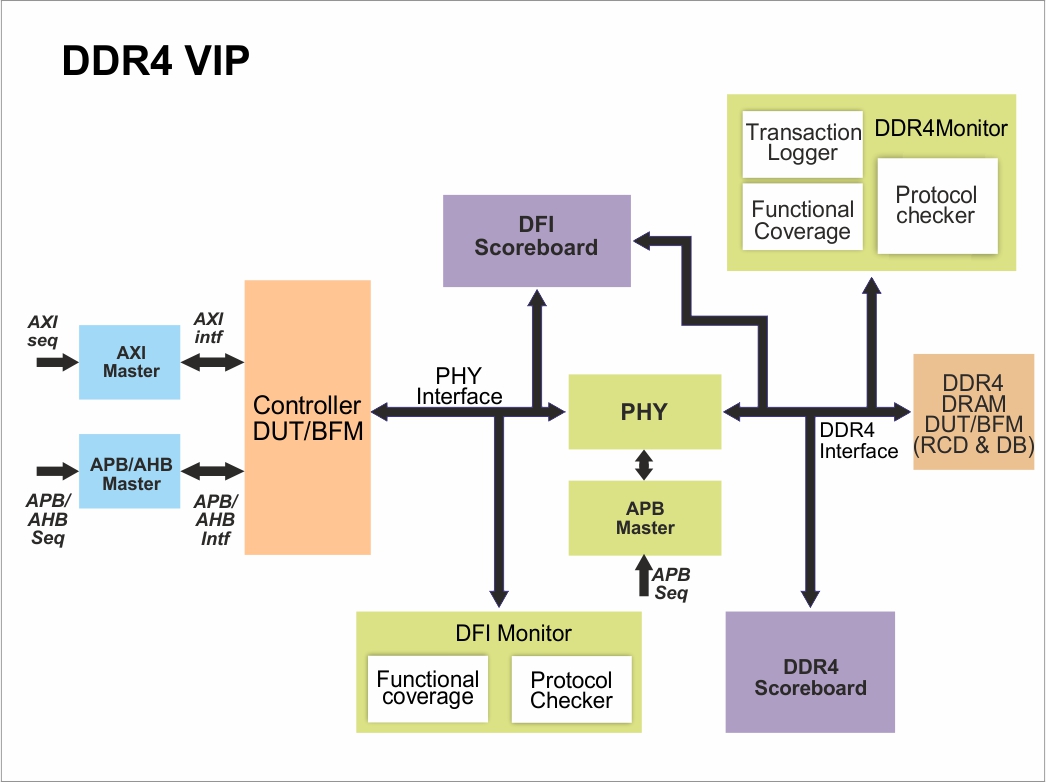

DDR4 Verification IP

Truechip's DDR4 Verification IP provides an effective & efficient way to verify the components interfacing with DDR4 interface of an ASIC/FPGA or SoC. Truechip's DDR4 VIP is fully compliant with Standard DDR4 Version JESD79-4B specification from JEDEC. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key Benefits

- Available in native SystemVerilog(UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Compliant to JEDEC DDR4 SDRAM Specification version JESD79-4B.

- Supports connection to any DDR4 Memory Controller IP communicating with a JESD79-4B compliant DDR4 Memory Model.

- Supports configurable SDRAM addressing of different sizes (x4,x8 and x16).

- Available in all memory sizes from 2 Gb to 16 Gb.

- 3DS Memory Model also available.

- Supports Data Bus Inversion(DBI).

- Supports Data Masking(DM).

- Supports CAL mode(CS_n to command address latency).

- Support for all speed-grades/speed-bins.

- Supports configurable timing parameters and rank associations.

- Supports capturing all the valid DDR4 commands including Activate, Read Write, Precharge.

- Supports CA parity for command/address bus.

- Supports Power-up Reset and initialization sequences.

- Supports Precharge Power-Down, Active Power-Down, Self-Refresh operation.

- Reports various timing errors, which can be used to check any timing violations.

- Provides full control to the user to enable / disable various types of messages.

- Supports full timing models or bus functional models.

- Support for Multiple Ranks architecture.

- Supports advanced SystemVerilog features like constrained random testing.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis. Ø Provides a comprehensive user API (callbacks) in Monitor, Controller and Memory Model BFMs.

- Graphical analyser to show transactions for easy debugging.

- Supports RCD, DB, RDIMM and LRDIMM.

Deliverables

- DDR4-SDRAM Model

- DDR4 Monitor & Scoreboard

- DDR4 Memory Controller BFM/Agent

- DDR4 PHY BFM model

- DDR4 Phy Monitor and Scoreboard

- Test-Bench Configurations

- Test Suite (Available in Source code)

- Basic Protocol Tests

- Directed & Random Tests Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes