eMMC 5.1 verification IP

Truechip's eMMC 5.1 Verification IP provides an effective and efficient way to verify the component interfacing with eMMC interface of an ASIC / FPGA / SOC. Truechip's eMMC verification IP has fully complied with standard eMMC version JESD84-B51 from JEDEC. This VIP is a Light Weight VIP with easy plug and play features.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites Ø 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Compliant to JEDEC eMMC version JESD84 - B51.

- Supports eMMC devices from all leading vendors.

- Supports configuration for both host and device.

- Support all data widths 1x, 4x, and 8x.

- Supports all speed modes (Legacy Speed Mode, High-Speed Mode).

- Support both Single Block and Multiple Block transfers.

- Supports Tuning. Ø Supports general-purpose commands.

- Supports Lock / Unlock feature.

- Supports Block Read and Block Write.

- Supports device density of Greater than equal to 2GB (Low Capacity and High Capacity).

- Supports both Normal Booting and Alternate Boot operation.

- Supports Sleep Mode and Sleep Notification.

- Supports the Reliable Write feature.

- Supports Write Protection Mechanism.

- Supports Multiple Partitions (Boot Area / User Area / General Purpose Partition).

- Support for both SDR and DDR.

- Supports Data Removal Commands Erase (High Capacity) / Trim / Sanitize / Discard.

- Supports Secure Erase/TRIM.

- Supports Replay Protect Memory Block (RPMB).

- Supports Background Operations.

- Supports High Priority Interrupt.

- Supports High-Speed Mode (HS200).

- Supports Enhanced Partition Types.

- Supports Power Off Notifications & Packed Commands.

- Supports Data tagging & Device Capacity.

- Supports Extended Security Commands.

- Supports High-Speed Mode (HS200, HS400).

- Supports Secure Removal Type & Enhanced Data Strobe.

- Supports Partitioning feature & Bus testing.

- Supports Power Saving Mode.

- Supports Power Off Notification.

- Supports Field Firmware Update.

- Supports Real-Time Clock.

- Supports all Device Statuses (Switch Error, CSD/CID Error, Block Length Error, etc).

- Supports Data Tag Mechanism.

- Supports Cache (Including Barrier & Flush Operation).

- Supports Production State Awareness.

- Supports the Context Management feature.

- Supports Hardware Resets and Software Reset (CMD0).

- Supports Sector Memory Organization.

- Support for full-timing as well as behavioral versions in one model.

- Supports for all timing delay ranges in one model min and max.

- Reports various timing errors, which can be used to check any timing violation.

- It provides full control to the user to enable/disable various types of messages.

- Supports advanced System Verilog features like constrained random testing.

- Supports dynamically configurable modes.

- Strong protocol monitor with a real-time exhaustive programmable check.

- Supports Dynamic as well as static error injection scenario.

- Built-in coverage analysis.

- Provides a comprehensive user API (callbacks) in monitor, host, and device controller models /BFM

- Graphical analyzer to show transactions for easy debugging.

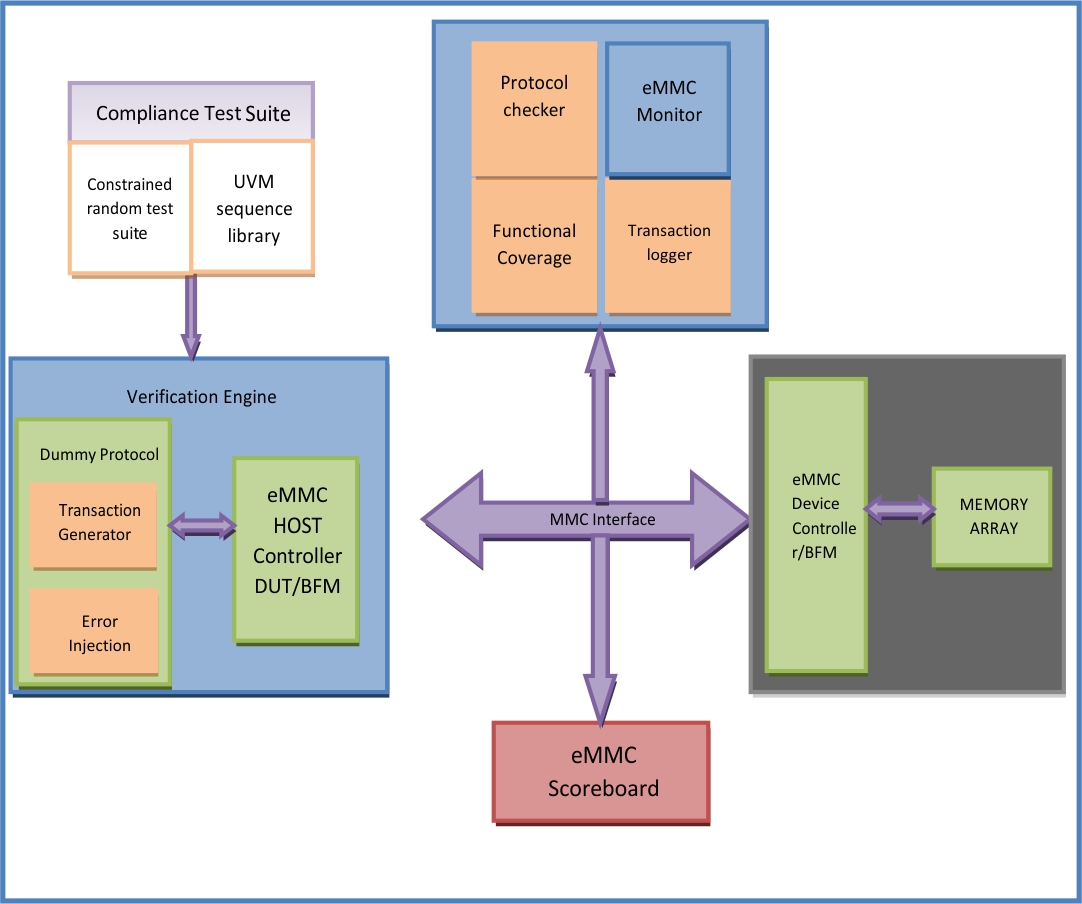

Deliverables

- eMMC Host controller BFM / Agent

- eMMC Device Controller / Memory BFM/DUT

- eMMC Monitor

- eMMC Scoreboard

- Test Bench Configurations

- Test suite available in source code

- Basic Protocol test

- Directed and random test

- Assertion and cover-point test

- Integration guide / User Manual /release notes

- GUI analyzer to view simulation packet flow