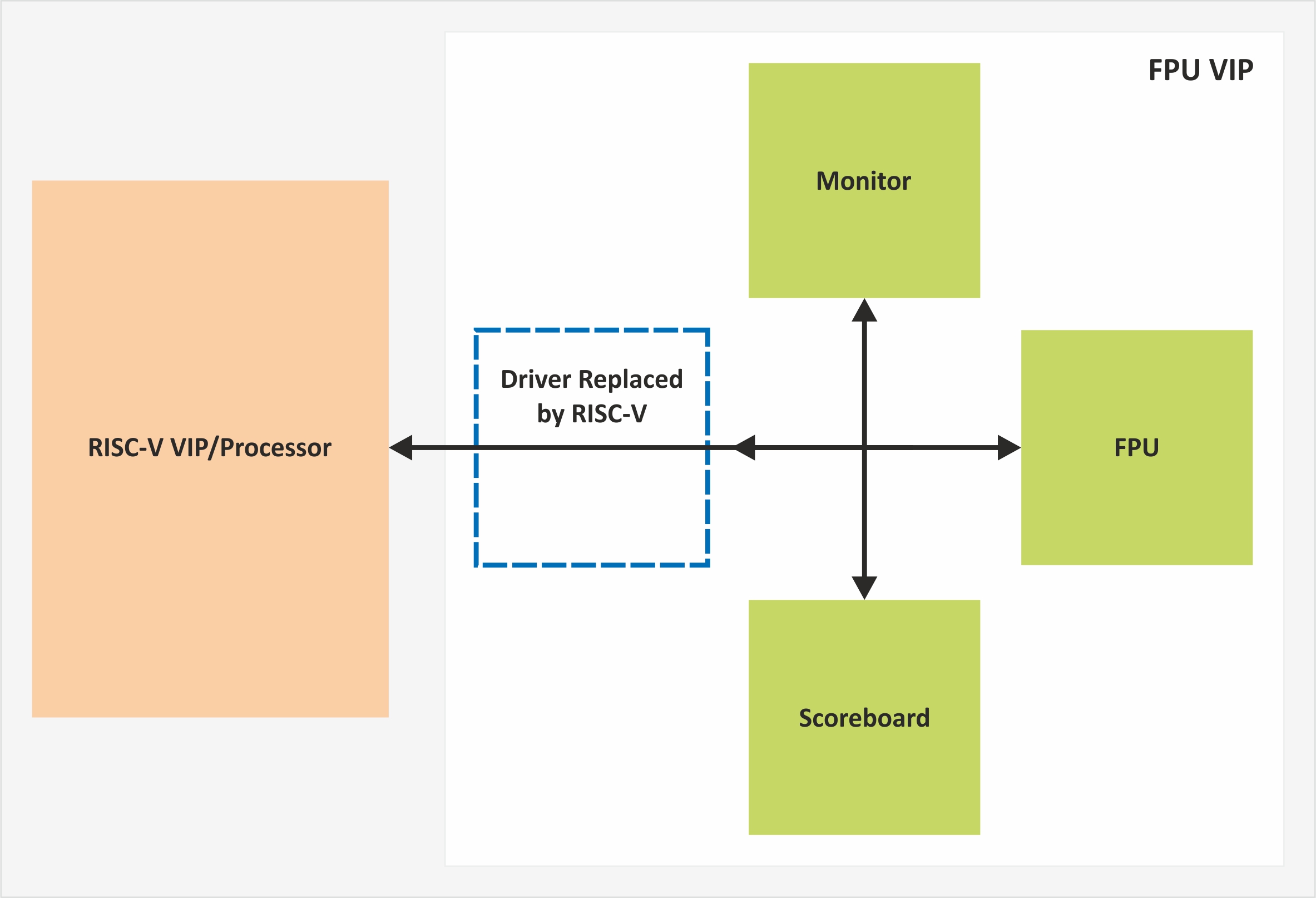

FPU Verification IP

Truechip's FPU Verification IP provides an effective & efficient way to verify the components interfacing with FPU interface with a RISC-V or other processor. Truechip's FPU VIP is fully compliant with Standard RISC-V specification. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key Benefits

- Available in native SystemVerilog, UVM and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Compliant to RISC-V Specification and IEEE 754 floating point standard.

- Configurable bits (half, single, double and quad precision).

- Supports all RISC-V Floating point instructions (ADD, SUB, MUL, DIV, SQRT, comparison, and conversion between float and int).

- Supports the rounding modes defined by RISC-V.

- Supports all exception flags.

- Support of NaN generation and propagation.

- Tests for corner scenarios (including zeros, infinity and NaN).

- Bus assertions for all possible scenarios.

- Support endianness checks and conversion.

- Supports UVM_RAL model.

- Provides detailed statistics for each transaction.

- Provides a comprehensive user API (callbacks) in all BFMs.

Deliverables

- FPU Master/Slave Agent.

- FPU Bus Monitor, assertion module and Scoreboard.

- Test Environment and Test Suite:

- Basic and directed protocol tests.

- Random Tests.

- Error Scenario Tests.

- Assertion and cover-point Tests

- Integration guide, User Manual, FAQ, and Release Notes.

- Graphical Analyzer for easy debugging and performance evaluator