PCIe Gen 6 Verification IP

Truechip's PCIe Gen 6 Verification IP provides an effective & efficient way to verify the components interfacing with PCIe Gen 6 interface of an IP or SoC Truechip's PCIe Gen 6 VIP is fully compliant with latest PCI Express Gen 6 specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Compliant with PCI Express Specifications 6.1 (64GT/s), 5.0 (32GT/s), 4.0 (16GT/s), 3.1 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Support for 64.0 GT/s Data Rate per lane with backwards compatible.

- Support for new PAM4 Signalling and Gray Coding.

- Support for both Flit Mode & Non-Flit Mode.

- Support for TS0 ordered set (Equalization at 64bit).

- Support for Precoding at 32GT/s and 64GT/s.

- Support for New Power Management state L0p.

- Configurable Link Width: x1, x2, x4, x8, x16 (x12 and x32 in Non-flit Mode)

- Supports Low Power management LTSSM states - L1, L2, L1 sub states, PCI- PM, ASPM.

- Compliant with latest PIPE Specification 6.2

- Supports SerDes PIPE Architecture as well as Original PIPE Architecture.

- Supports Low Pin Count Interface as well as Legacy PIPE Interface.

- Configurable PIPE width support:

- Original PIPE Arch. - 8, 16, 32, 64

- SerDes PIPE Arch. - 10, 20, 40, 80

- Support for Shared Flow Control Mechanism.

- Supports 14-bit Tag as requester as well as completer.

- Supports Non-Posted Deferrable Memory Writes.

- Advanced Error Reporting (AER) with optional Malformed TLP checks, ECRC and TLP Poisoning support.

- Support for optional extended capabilities such as

- Flit Error Injection Extended Capability

- VF Resizable Bar Extended Capability

- Data Object Exchange Extended Capability

- Supports simplified replay timer and SR-IOV

- Support for ATS with latest ATS Specification v1.1

- Supports LTR & FLR (Function Level Reset).

- Support for SSC and Jitter in clock.

- Support for Common RefClk and Separate RefClk

- Compliance testing in TL, DLL & PL including power management test-suites.

- Support for Flit Logging Ext ended Capability.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis.

- Provides a comprehensive user API (call backs)

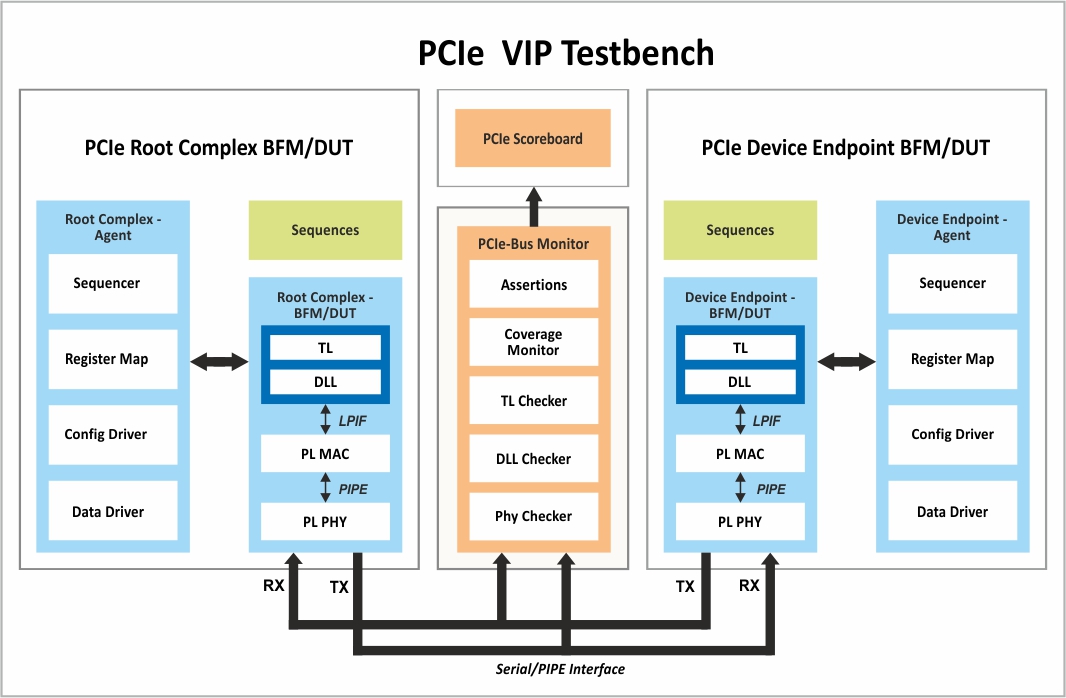

- Verification IP configurable as PCI express Root Complex, Device Endpoint or PCIe Switch.

- Support for Block Level Verification.

- Graphical analyser for all three Layers to show PCIe transactions for easy debugging.

Deliverables

- PCIe Gen 6 Root-Complex/Device-Endpoint

- PCIe Gen 6 BFM/Agents for:

- PHY Layer

- Data Link Layer

- Transaction Layer

- Register Space

- PCIe Gen 6 Layered Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random TestsError Scenario Tests

- Assertions & Cover Point Tests

- Compliance Tests

- Integration Guide, User Manual, and Release Notes