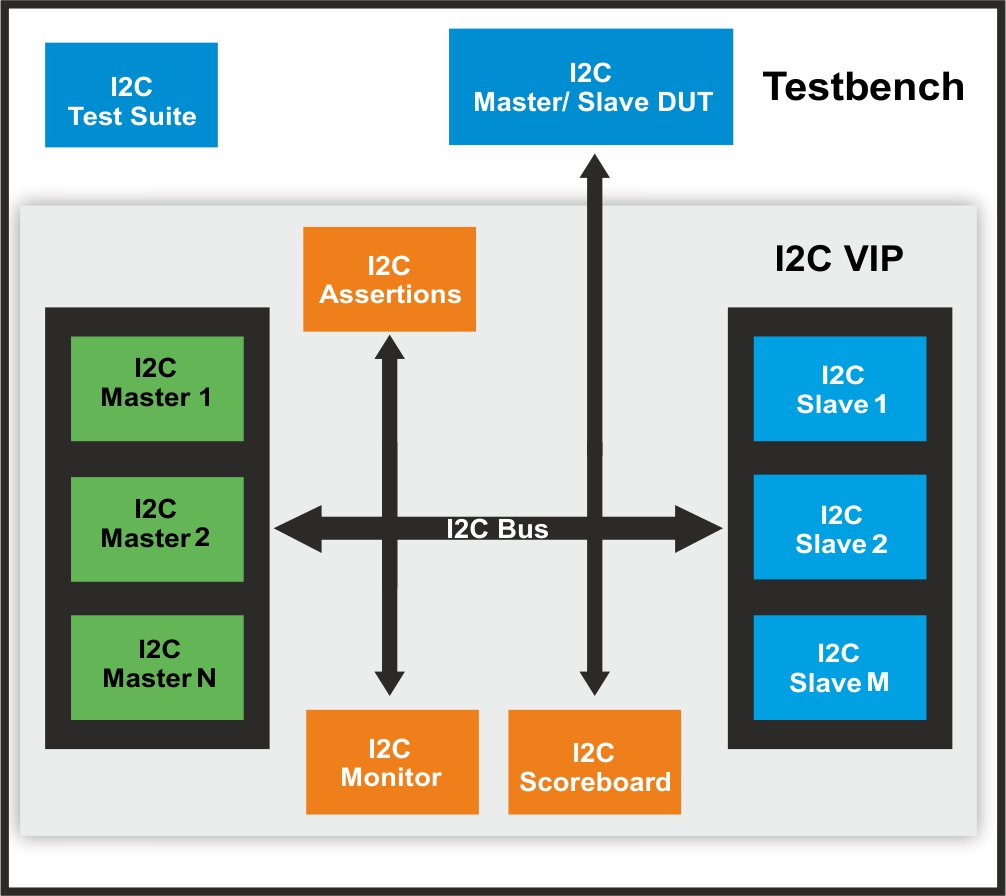

I2C/I2S Verification IP

Truechip's I2C Verification IP provides an effective & efficient way to verify the components interfacing with I2C interface of an IP or SoC. Truechip's I2C VIP is fully compliant with Rev. 6 of I2C specifications from Philips. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest level of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

Features

- Fully compliant with Rev. 6 of the I2C-Bus Specification and backward compatible upto 2.1 version

- Full I2C Master and Slave functionality

- Master Transmitter/Master Receiver

- Slave Transmitter/Slave Receiver

- START, repeat START and STOP for all possible transfers

- Supports all Speed Modes: Standard Speed Mode (upto 100 kb/s), Fast Speed Mode (upto 400 kb/s), Fast Speed Mode Plus (upto 1Mb/s) and High Speed Mode (upto 3.4 Mb/s), Ultra fast mode (upto 5Mb/s)

- Supports 7-Bit and 10-Bit addressing format

- Allowstesting of varied bustraffic for Read, Write, General Call

- Supportsscoreboard feature for end to end data integrity check

- Notifies the Testbench of significant events such as transactions, warnings, and protocol errors

- Built in I2C Bus Monitor provides extensive protocol checking

- Supports Multi-Master and Multi-Slave system

- Supports Arbitration and Clock Synchronization

- Supports START Byte, Device ID, Bus Clear and Clock Stretching

- Supports various error injection and detection

- Provides verification scalability using functional coverage

- Provides logging facility for bus traffic in the ASCII format and in user configurable mode

- Supports Callback in Master and Slave

- Supports timing checks in the Monitor

- Supports UVM_RAL Model

- Supports CCI mode

- Supports transaction logging with detailed description of each transfer

Deliverables

- I2C Master / Slave Agent

- I2C Monitor and Score board

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Notes