I2S Verification IP

Truechip's I2S Verification IP provides an effective & efficient way to verify the components interfacing with I2S interface. Truechip's I2S VIP is fully compliant with the Standard I2S Version.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest level of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environments.

Features

- Supports Full-duplex (transmit and receive) communication.

- Double buffered data registers that allow for continuous data stream.

- Most significant bit (MSB) - first data transfers.

- Supports I2S/Left-justified and DSP serial data communication formats with a data delay of 1 or 2 bits.

- Supports Data word-lengths of 8, 10, 12, 14, 16, 18, 20, 24, or 32 bits.

- Ability to sign-extend received data samples for easy use in signal processing algorithms.

- Supports Ability to pack multiple data words into CPU or DMA-accessible data registers to reduce interrupts for more efficient operation.

- Supports Programmable polarity for both frame synchronization and bit-serial clocks.

- Supports Digital loopback of data from transmit to receive data register(s) for application code debug.

- Supports Stereo (in I2S/Left-justified or DSP data formats) or mono (in DSP data format) mode.

- Supports Programmable divider for serial data clock (bit-clock) generation when I2S bus used as a master device.

- Supports Programmable divider for frame sync clock generation when I2S bus is used as the master device.

- Supports Detection of over-run, under-run, and frame�synchronization error conditions.

- Supports The DSP includes four independent I2S modules.

- Supports Provides full control to the user to enable/disable various types of messages

- Supports Integrates easily in any verification environment

- Supports advanced SystemVerilog features like constrained random testing

- Supports Error Injection scenarios

Deliverables

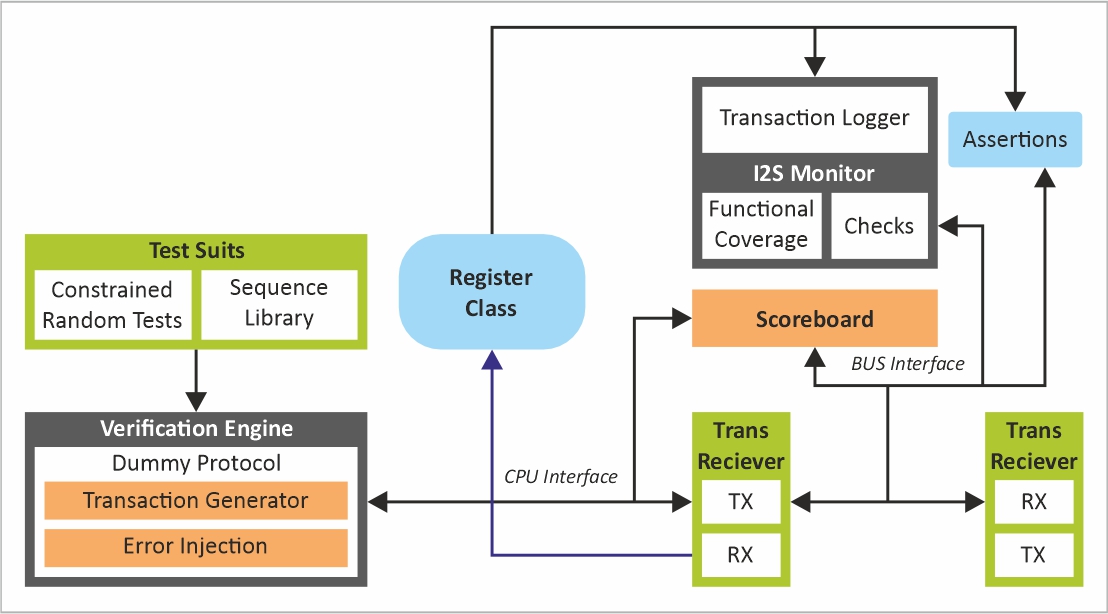

- I2S BFM's for :

- I2S monitor & scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Compliance Test Suite

- User Test Suite

- Integration Guide, User Manual and Release Note