I3C 1.1.1 Verification IP

Truechip's I3C Verification IP provides an effective & efficient way to verify the components interfacing with I3C interface of an IP or SoC. Truechip's I3C VIP is fully compliant with Rev. 1.1.1 of I3C specifications from MIPI. This VIP is a lightweight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest level of quality

- Availability of Conformance and Regression Test Suites

- 24x5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Fully compliant with Rev. 1.1.1 of the I3C-Bus Specification

- Support existent I2C bus/device. like I2C messaging, Single Data Rate messaging (SDR), etc.

- Support all type of speed modes.

- Support Broadcast or directed (Common Command Code) command to the slave.

- Same master capable of sending I2C Transfers also.

- Vip’s master BFM can connect to I2C Slave Devices.

- Legacy I2C Device co-existence on the same Bus of I3C.

- Dynamic Address allocation.

- In-Band Interrupt support

- Support Multi Master and Slave

- Can work as secondary master on request.

- Maximum 11 Slave can be configured.

- Supports additional Multi-Drop and Hot-Join capability

- Support all type of roles for slave(SDR only slave and with SDR & HDR mode).

- Supports Arbitration and Clock Synchronization.

- Supports generation of transactions with UVM register model.

- Built in I3C Bus Monitor provides extensive protocol checking.

- Supports various error injection and detection.

- Provides verification scalability using functional coverage.

- Provides logging facility for bus traffic in the ASCII format and in user configurable mode.

- Supports timing checks in the Monitor.

- Callbacks for user-defined transfers.

- Supports transaction logging with detailed description of each transfer.

- Graphical analyser to show transactions for easy debugging.

Deliverables

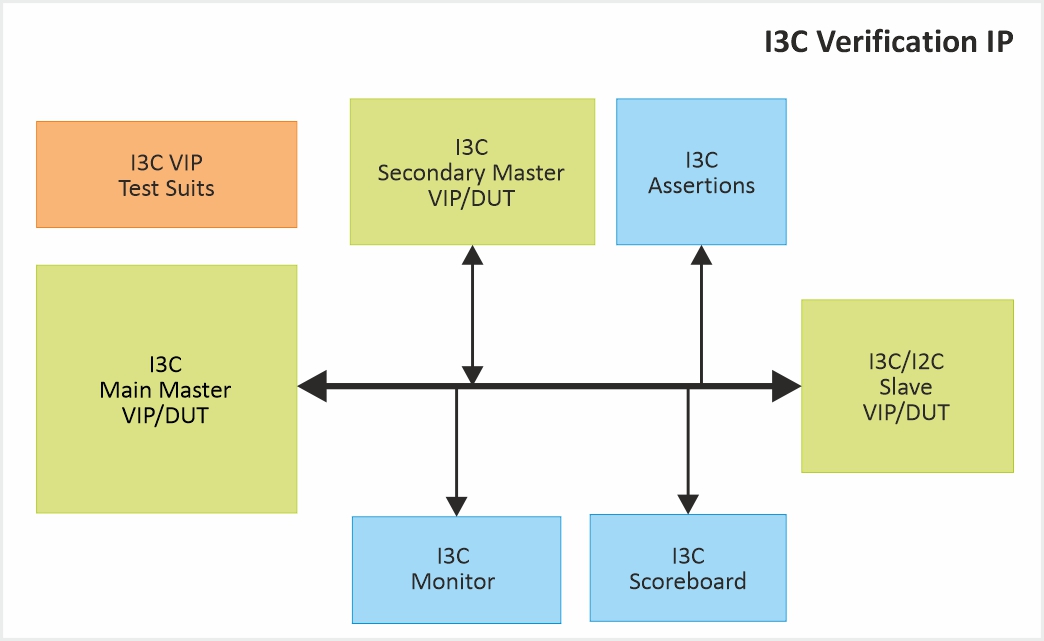

- I3C Master/Slave Agent

- I3C Monitor and Score board

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes