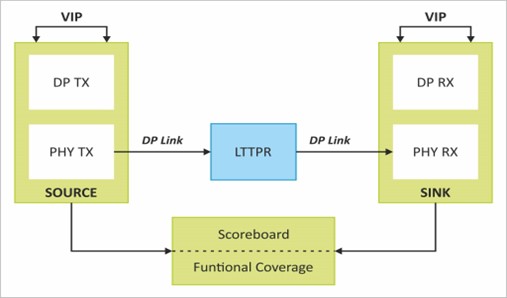

LTTPR Verification IP

Truechip's DisplayPort Verification IP provides an effective & efficient way to verify the components interfacing with the DisplayPort interface of an ASIC/FPGA or SoC. Truechip's Display port VIP LTTPR component is fully compliant with Standard DisplayPort Version 1.4a/2.0/2.1 specifications from VESA This VIP is a lightweight VIP with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- Supports 8b/10b encoding and 128/132b encoding.

- LTTPR is compliant with DP1.4, DP2.0, and DP2.1.

- DisplayPort VIP Supports Singe as well as Multi LTTPR environment.

- LTTPR supports FEC encoding and decoding.

- LTTPR is capable of bypassing the training patterns and generating its own training patterns.

- Link Training in LTTPR Transparent mode supported.

- Link training in LTTPR Non-Transparent mode supported.

Deliverables

- Source - Link-Layer Source - MAC Layer

- Source - PHY Layer Sink - Link Layer

- Sink - MAC Layer Sink - PHY Layer

- LTTPR Devices

- DisplayPort layered monitor & scoreboard

- Test Environment & Test Suite :

- Basic and Directed Protocol Tests

- Random Tests and Error Scenario Tests

- Assertions & Cover Point Tests

- Compliance Test Suite User Test Suite

- Integration guide, user manual, and release notes

- GUI analyzer to view simulation packet flow