Crossbar IP

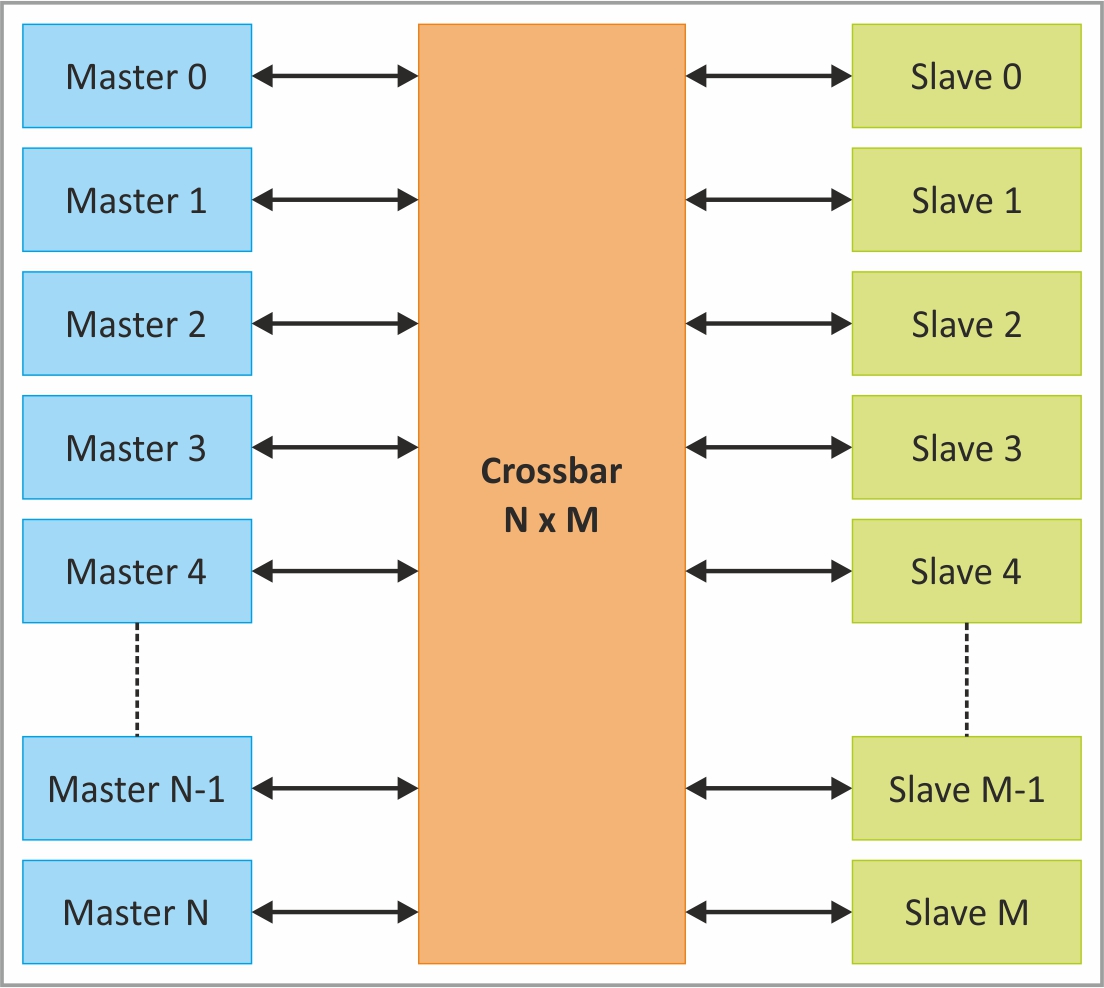

Truechip's NoC Crossbar Silicon IP provides chip designers and architects with an efficient way to connect multiple protocol bus protocol supportive devices with reduced latency, power, and area.

It provides hardware cache coherency with software cache maintenance, NoC Silicon IP also helps to reduce the usage ofinterconnecting wires and resources inside the chip.

Key Benefits

Deliverables

- NoC Matrix

- Crossbar

- Mesh

- Coherent Crossbar

- Coherent Mesh

- NoC Port (AXI/AHB/APB/Tilelink)

- Ip generator & config tool

- Verilog Test Environment with Verilog Testcases

- CDC constraints file (.sdc)

- IP analysis reports

- Linting report

- Synthesis report

- CDC report

- Simulation script

- IP Block Guide

- IPG Guide

Features

Noc Crossbar Features

- Complex network with acyclic agent graph (DAG) also layered and parallel NoC supported.

- Network interface blocks can be separated

- Multiple levels of NoC using multiple instances

- Any number of master and slave ports is supported. Each port can be configured individually.

- AMBA 5,4,3 AXI, AXI-Stream, AHB, APB Tilelink UL & UH

- Configurable memory map for different access types of memory regions.

- Support for different protocols for master and slave port interface.

- Each port data width can be different also other protocol supported signals can also have different widths.

- Early response and interrupt generation each port

- Configurable channels for data transfer

- Configurable arbitration modes to select (fixed/round robin)

- Merging and breaking both possible on transfers

- Support different phase shifted frequencies for each Master & Slaves

- Clock gating mechanism is supported

- QoS supported: port priority, programmable register, Keeper count

- Both little and high endianness is supported

- Register slice for asynchronous interface is supported

- req or rsp can propagate through NoC in minimum latency

- Configurable outstanding for read and write transfer separately

- Per port reset is supported

- Operation Mode are available such as Placement friendly, Low Congestion, dynamic Low Power consumption, Latency friendly

Noc Port Features

- Configurable access methods, port security and privilege option supported

- Configurable default slave and port Priority supported

- Different protocol with different phase shifted clock supported for each port

- Configurable option for Read OT and Write OT (Outstanding transaction).

- Atomic transaction, NSAID signalling, Read data chunking, Interleaving support, out of order transfer, Exclusive supports in AXI port

- Secure transfer

- Beat transfer

- Non-contiguous address

- Arithmetic and logical transfer

- Back-to-back transfer supports in AHB

NoC Mesh Silicon IP

Truechip's NoC Mesh Silicon IP provides chip designers and architects with an efficient way to connect multiple protocol bus protocol supportive devices with reduced latency, power, and area.

It provides hardware cache coherency with software cache maintenance, NoC Silicon IP also helps to reduce the usage ofinterconnecting wires and resources inside the chip.

Key Benefits

- Available in native Verilog (RTL).

- Linting, Synthesis, CDC, RDC are cleaned up.

- 100% Code coverage.

- Verified with an expert team using comprehensive and Regression Test Suites.

- Consistency of interface, installation, operation, and documentation across all our IP.

- Easy GUI based integration and configuration technique.

- 24X5 customer support.

- Unique and customizable licensing models.

Deliverables

- NoC Matrix

- Crossbar

- Mesh

- Coherent Crossbar

- Coherent Mesh

- NoC Port (AXI/AHB/APB/Tilelink)

- Ip generator & config tool

- Verilog Test Environment with Verilog Testcases

- CDC constraints file (.sdc)

- IP analysis reports

- Linting report

- Synthesis report

- CDC report

- Simulation script

- IP Block Guide

- IPG Guide

Features

Noc Mesh Features

- Complex network with acyclic agent graph (DAG) also layered and parallel NoC supported.

- Robust routing algorithm to traverse data in efficiently.

- Network Interface blocks can be separated.

- Any number of master and slave ports is supported, each port can be configured individually.

- AMBA 5,4,3 AXI, AXI-Stream, AHB, APB Tilelink UL & UH

- Additional connections for reducing latency

- Deadlock avoidance guarantee

- Configurable node storage capacity

- Configurable memory map for different access types of memory regions.

- Support for different protocols for master and slave port interface.

- Each port data width can be different also other protocol attributes supported.

- Early response and interrupt generation possible

- Configurable channels for data transfer

- Merging and breaking both possible on transfers

- Support different phase shifted frequencies for each Master & Slaves

- clock gating mechanism is supported

- QoS supported: port priority, programmable register

- Both Little and high endianness is supported

- Register slice for asynchronous interface is supported

- Support physical address conversion through NOC

- Configurable outstanding for read and write transfer separately

- Per port reset is available

- Operation mode are available such as placement friendly, low Ccongestion,

- dynamic low power consumption, Latency friendly

Noc Port Features

- Configurable access methods, port security and privilege option supported

- Configurable default slave and port Priority supported

- Different protocol with different phase shifted clock supported for each port

- Configurable option for Read OT and Write OT(Outstanding transaction).

- Atomic transaction, NSAID signalling, Read data chunking, Interleaving support, out of order transfer, Exclusive supports in AXI port

- Secure Transfer

- Beat Transfer

- Non-contiguous address

- Arithmetic and logical transfer

- Back-to-back transfer supports in AHB

- Each transaction is marked with unique ID to identify the packet in Mesh