NVMe 2.0 Verification IP

Truechip's NVMe 2 Verification IP provides an effective & efficient way to verify the components interfacing with CXL interface of an IP or SoC. Truechip's NVM 2 VIP is fully compliant with the latest NVMe specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Compliant with the NVMe 2, 1.4, 1.3, 1.2 specification.

- Compliant with PCI Express Specifications 6.0 v1.4(64GT/s), 5.0 v1.0(32GT/s), 4.0 v1.0 (16GT/s), 3.0 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Compliant with PIPE Specification 6.0,5.1, 4.4.1.

- NVMe on top of Low Power, CXS, CPI, CXL, CXL Security, PCIe Gen6/5/4/3 management

- Fully categorized test plan for all kinds of NVMe commands.

- Supports fused operation.

- Supports the on the fly queue creation and deletion.

- Support for NVMe subsystem Reset.

- Supports for PRP and SGL for data transfer.

- Support for queue priority.

- Supports all mandatory commands.

- Configurable number of outstanding Abort and Asynchronous commands.

- Supports multiple Namespaces.

- Support for Namespace Attachment, Namespace Management and Format NVM commands.

- Configurable number of IO completion and submission queues with configurable number of queue size.

- Support for MSI, MSIx and PIN based interrupt mechanisms.

- Support for Verify command.

- Truechip proprietary Address mapping for SSD address mapping.

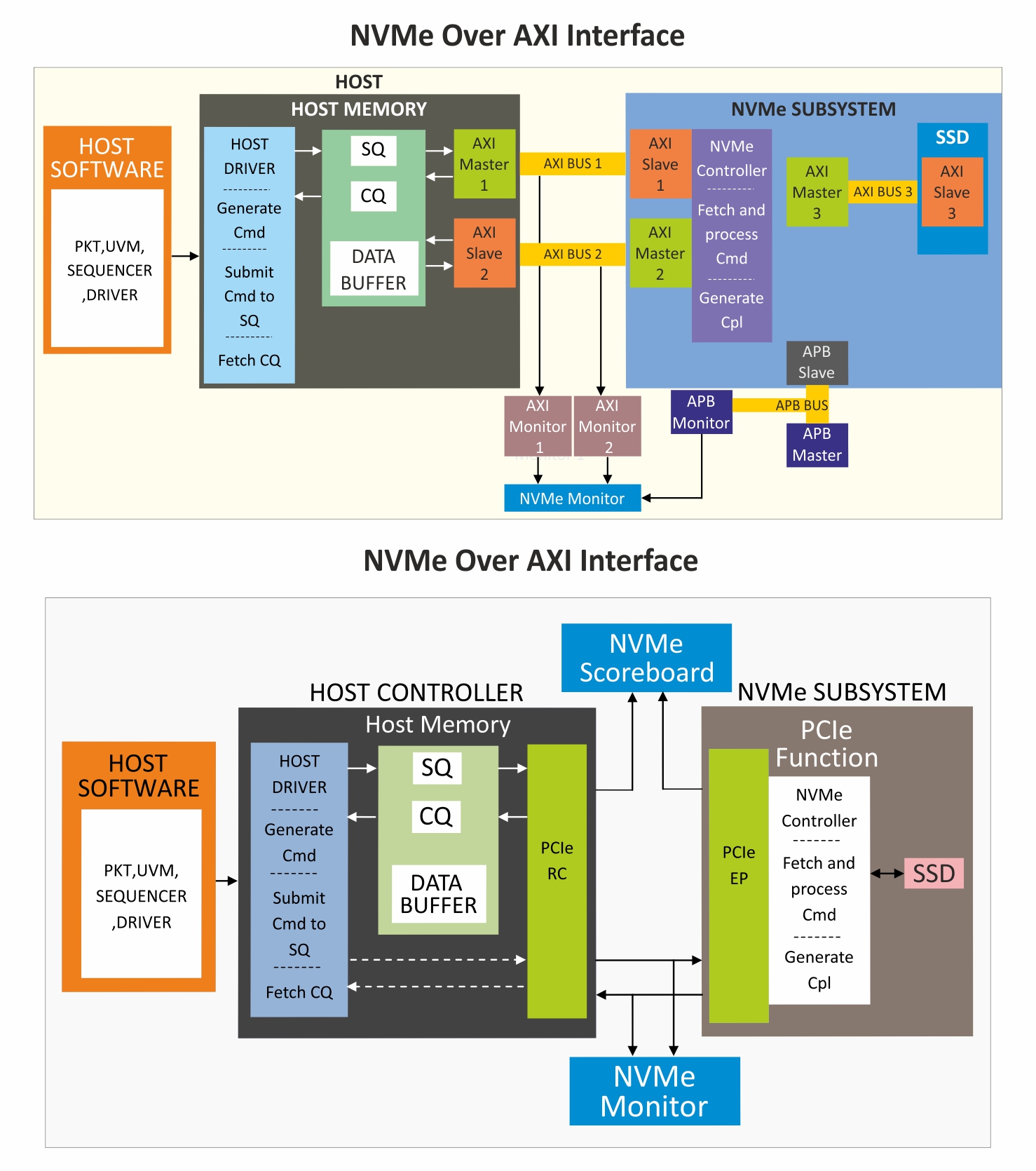

- Both AXI bus and Truechip proprietary bus for transferring data to SSD are supported.

- Supports for Host Memory Buffer feature with configurable host memory size and number of hosts.

- All Directive commands with both Identify and Stream Directive types are supported with a configurable number of stream resources.

- Support for Sanitize command with all the three supported sanitize methods.

- Support for Telemetry.

- Support for NVM sets, PMR regions and Read recovery levels.

- APB Support to configure DUT registers.

- Supports for Virtualization with configurable number of controller on virtual function.

- Support for Metadata Handling.

- End-to-end data protection (T10 DIF and DIX compatible).

- Security sends and receives command support.

- Firmware update and activation.

- Support for Autonomous power management.

- Robust error reporting.

- Interrupt coalescing configuration control.

- Capability discovery and configuration.

- Up to 64K I/O queues each with up to 64K entries.

- Fixed-size 64B submission commands and 16B completions enable fast and efficient command decode and execution.

- Supports advanced SystemVerilog features like constrained random testing.

- Supports dynamically configurable modes

- Support for NVME MI 1.0 specification version

- Complaint with UNH-IOL NVMe Conformance v13.0

Deliverables

- NVM EXPRESS Host/ NVMe Controller

- NVM EXPRESS Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests and Error Scenario Tests

- Assertions & Cover Point Tests

- Compliance Tests

- Documents:

- Integration Guide

- User Manual

- Quick Start Guide, Release Notes

- FAQs