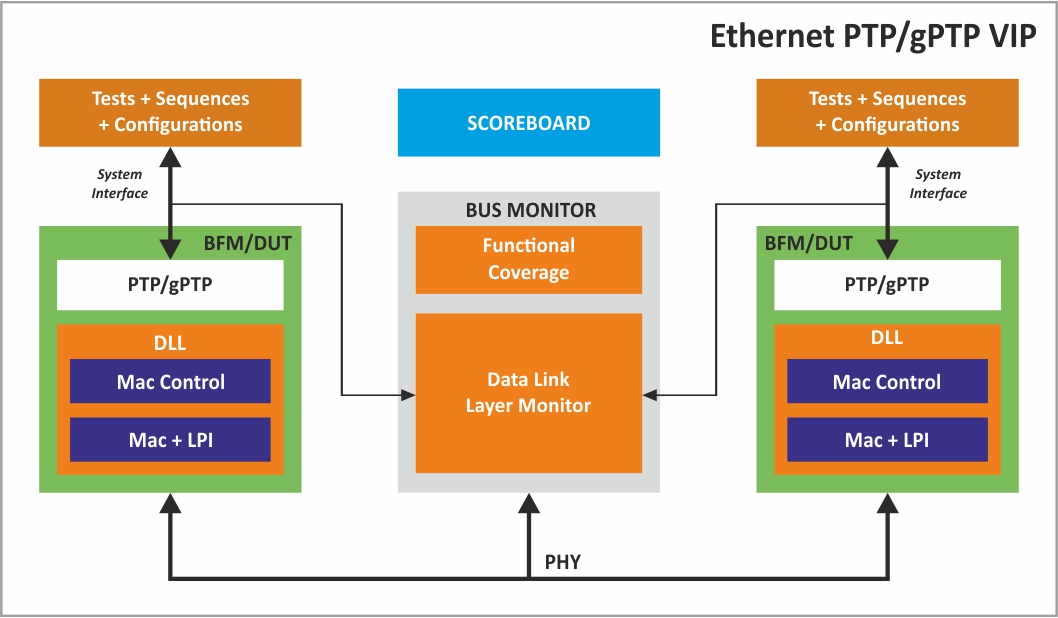

PTP/gPTP Verification IP

Truechip's PTP/gPTP Verification IP provides an effective & efficient way to verify the components interfacing with PTP/gPTP interface of an IP or SoC. Truechip's PTP VIP is fully compliant with IEEE 1588-2008 specification and gPTP VIP is fully compliant with IEEE 802.1AS-2011 specification. This VIP is lightweight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- Provides Ethernet fully compliant to 802.3-2018 supporting all media independent interfaces for (1/10/25/40/50/100/200/400/800 G)

- Provides PTP as per IEEE 1588-2008 specification

- Supports BMCA

- Supports PTP Delay Request Mechanism (Announce-sync-FollowUp-DelayReq-DelayResp)

- Supports PTP Peer Delay Mechanism (PdelayReq – PdelayResp - PdelayRespFollowUp)

- Supports Local Clock generation with user configurable start for timestamp generation

- Supports Master-Slave and slave only port state machines capable with support for all message timers

- Supports basic Management Messages with user control from test/sequence

- Supports one step and two step clock timestamping

- Provides gPTP as per IEEE 802.1AS-2011 specification

- Supports time-aware end stations

- Supports all types of Messages (Announce-sync-FollowUp-Pdelay Req – PdelayResp – PdelayRespFollowUp-signalling)

- Supports Peer Delay Mechanism and Mean Propagation delay calculation using peer delay messages

- Supports timestamping at the gPTP level with information for the local clock

- Supports BMCA(priority vector calculation and comparison) with determination of selectedRole

- Supports Local Clock generation with user configurable start for timestamp generation

- Supports clock data recovery(CDR).

- Supports test pattern generation and checking.

- Supports Management data Input/output registers.

- Supports full-duplex operation.

- Callback support in all Layers to provide user control.

- Rich set of configuration and parameters.

- Supports Dynamic as well as Static Error Injection scenarios.

- Built-in Coverage analysis.

- Graphical analyzer to show transactions for easy debugging.

Deliverables

- Deliverables PTP/gPTP BFM's for

- PTP layer

- gPTP layer

- MAC layer (optional)

- PTP/gPTP monitors and scoreboard

- Mac monitors and scoreboard (optional)

- Test environment and Test Suite-

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- User Test Suite

- Integration Guide, User Manual, and Release Note

- GUI analyzer to view simulation packet Flow