SpaceWire Verification IP

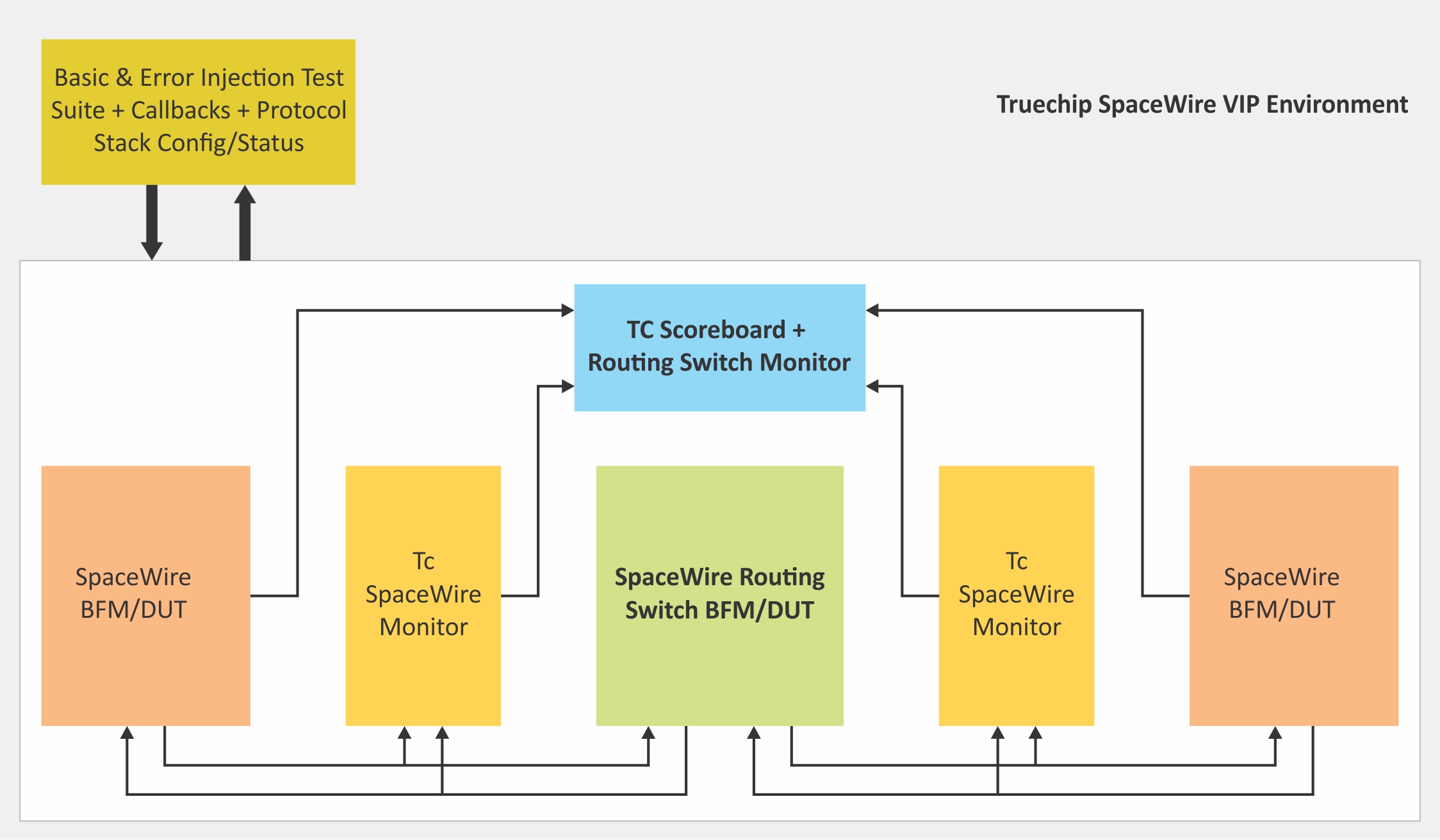

Truechip's SpaceWire Verification IP provides an effective & efficient way to verify the components interfacing with SpaceWire interface of an ASIC/FPGA or SoC. Truechip's SpaceWire VIP is fully compliant with ECSS-E-ST-50-12 C rev 1 specification of SpaceWire. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Available in UVM, System Verilog.

- Compliant to Specification ECSS-E-ST-50-12 C rev 1.

- Supports speeds between 2Mb/s to 400Mb/s

- Supports full duplex Serial data communication links

- Supports all Layers: Physical Layer, Encoding Layer, Data-link Layer, Network Layer, Management information base and service interfaces

- Supports Serialization and De-serialization.

- Supports Data-Strobe (DS) encoding and decoding

- Supports Character and control code encoding

- Supports flow control and link Initialization.

- Supports Broadcast codes, Time-codes, nodes and routing

- Supports sending packets of information from a source to a specified destination node.

- Supports encoding/decoding Link interface. Ø Supports all types of errors insertion/detection as given below:

- Link Error

- Network Error

- Disconnect Error

- ESE Error (Escape Sequence Error)

- Character Sequence Error

- Parity Error

- Destination Address Error

- Empty Packet Error

- Credit Error

- Provides link error recovery.

- Supports the exchange of silence error recovery procedure.

- On-the-fly protocol and data checking.

- Notifies the test bench of significant events such as transactions, warnings and protocol violations.

- Status counters for various events on bus.

- Built in functional coverage analysis.

- SpaceWire Verification IP comes with complete testsuite to verify each and every feature of SpaceWire specification.

- Provides full control to the user to enable / disable various types of messages.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Transmitter and Receiver.

- Graphical analyzer to show transactions for easy debugging.

Deliverables