UART/USART Verification IP

Truechip's UART /USART Verification IP provides an effective & efficient way to verify the components interfacing with UART/USART interface of an ASIC/FPGA or SoC. Truechip's UART/USART VIP is fully compliant with the Standard National Semiconductor PC16550D specification of UART/USART. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Available in UVM, System UVM, UVM.

- According to the National Semiconductor PC16550D Compliance.

- Supports Simplex and Duplex mode.

- Independently controlled transmit, receive, line status, and data set interrupts

- A programmable baud generator divides any input clock by 1 to (2^16 – 1) and generates baud clock according to the spec.

- Both 16x and 13x sample mode supported.

- Independent receiver clock input.

- Full duplex operation.

- MODEM control functions (CTS, RTS, DSR, DTR, RI and DCD).

- Fully programmable serial-interface.

- 5-, 6-, 7-, or 8-bit characters.

- Even, odd, or no-parity bit generation and detection.

- 1, 1.5 or 2 stop bit generation.

- UART/USART VIP can act as either UART/USART receiver or UART/USART transmitter in a transfer depending on the configurations set.

- Baud generation (DC to 1.5M baud).

- False start bit detection.

- Complete status reporting capabilities.

- Line breaks generation and detection.

- Configurable receiver FIFO depth.

- Reports various timing errors, which can be used to check any timing violations.

- Provides full control to the user to enable/disable various types of messages.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Transmitter and Receiver.

- Graphical analyzer to show transactions for easy debugging.

Deliverables

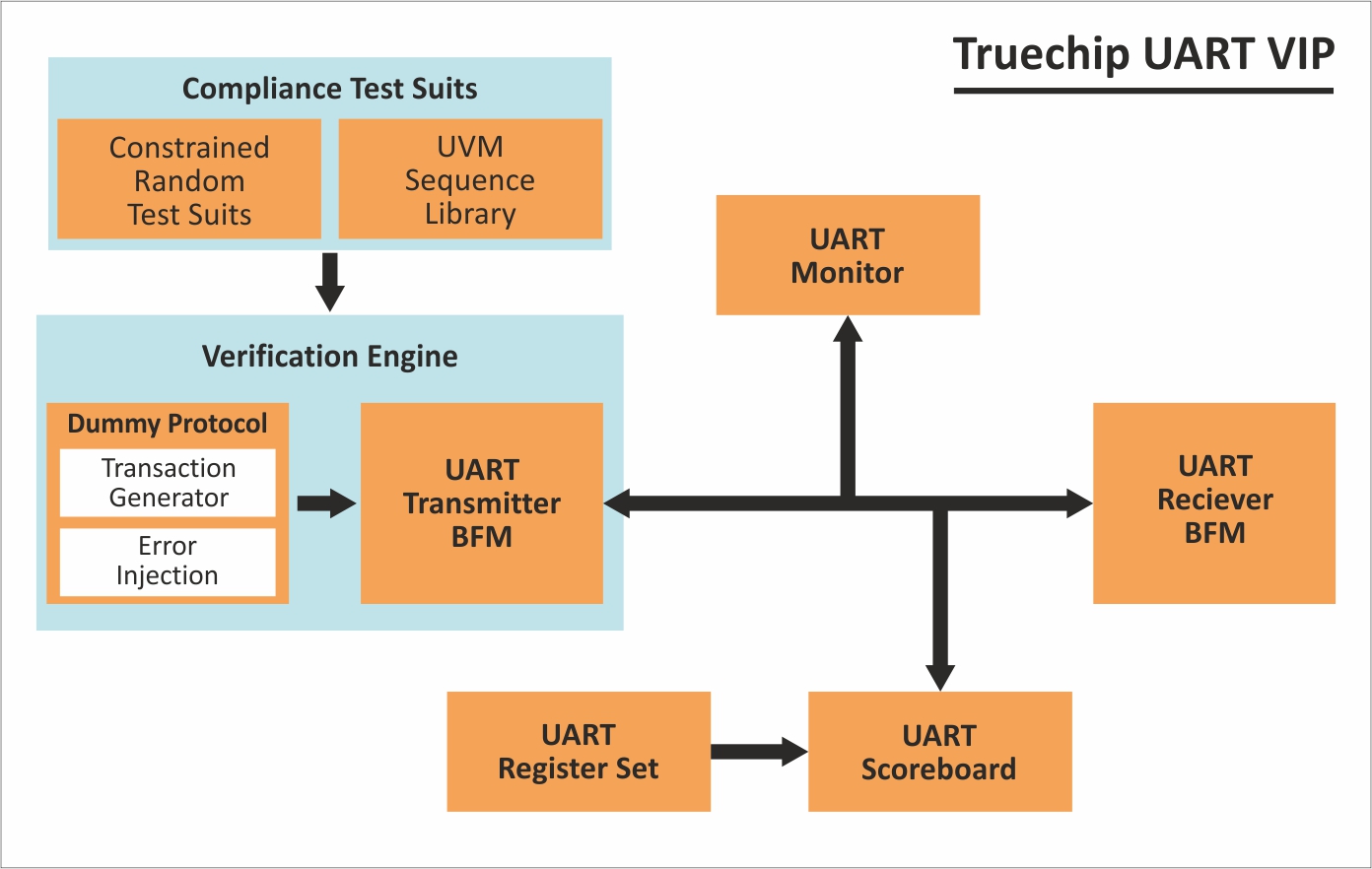

- UART/USART TRANSMITTER

- UART/USART Receiver

- UART/USART Monitor

- UART/USART Scoreboard

- Basic Test Suite

- Error Test Suite

- User Test Suite

- Integration Guide, User Manual, and Release Notes