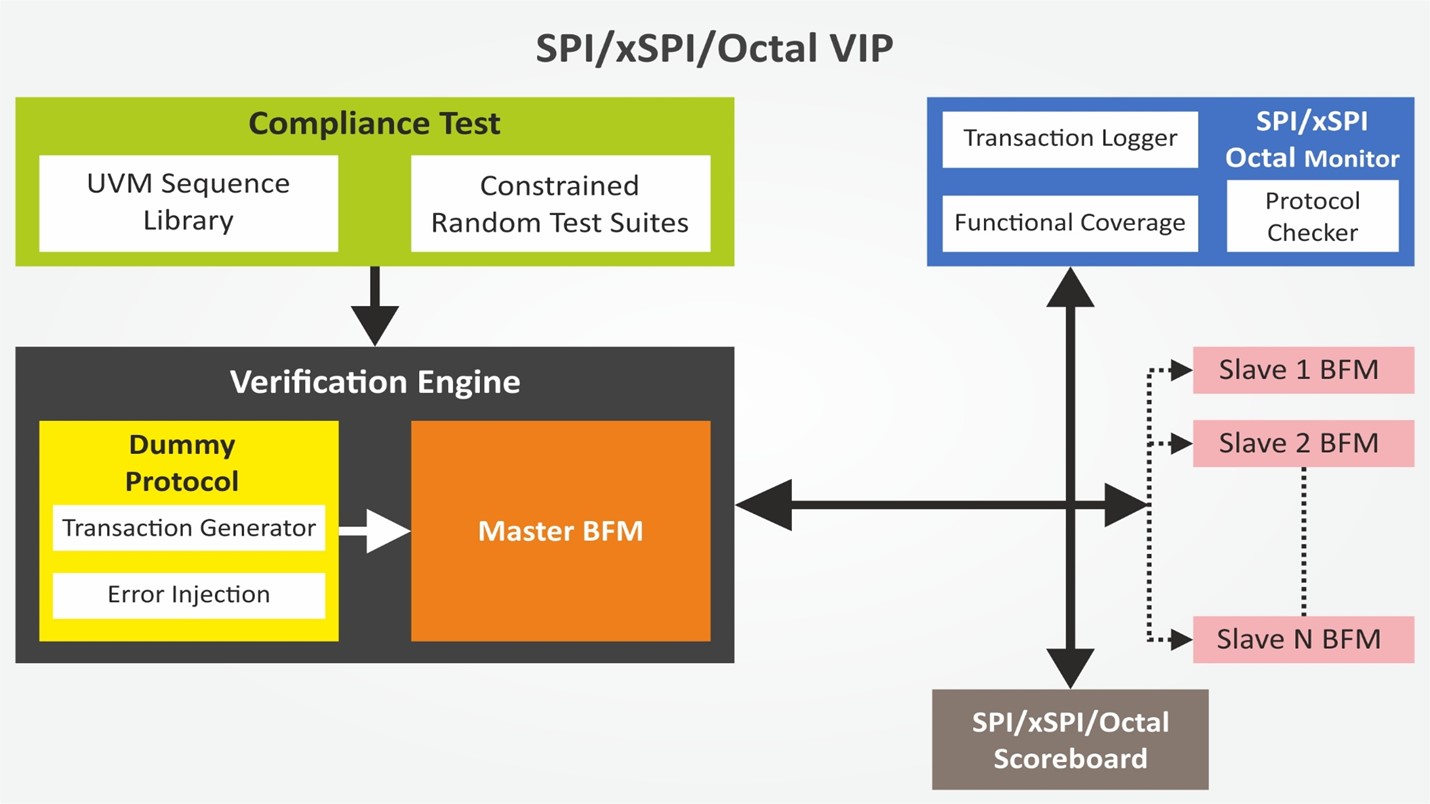

xSPI/SPI Verification IP

Truechip’s xSPI/SPI verification IP provides an effective and efficient way to verify the components (data converters and/ or logic devices) connecting with xSPI/SPI link. Truechip’s xSPI/SPI VIP is fully compliant with SPI Specification 512Mbit(64Mbyte) 3.0V SPI FLASH MEMORY S25FL5122 and also Compliant with JEDEC JESD251A expanded serial peripheral interface specification with the help of JEDE JESD216D-01 SFDP specification. This VIP is lightweight VIP with an easy plug-and-play interface so that there is no hit on the design time.

Key Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

Features

- Compliant to SPI Specification 512Mbit(64Mbyte) 3.0V SPI FLASH MEMORY S25FL5122

- Compliant with JEDEC JESD251A expanded serial peripheral interface specification with the help of JEDEC JESD216D-01 SFDP specification.

- Supports connection to any SPI Memory and SPI Master IP communicating with a CYPRESS spi flash memory model.

- Supports configurable timing parameters and multi-slave configurations.

- Supports multi-slave memory.

- Provides full control to the user to enable/disable various types of messages.

- Integrates easily in any verification environment.

- Supports full-timing models or bus functional models.

- Supports advanced System Verilog features like constrained random testing.

- Supports Callback/ User Configuration in all components.

- Supports ECC.

- Support Mode 0 (CPOL=0) and Mode 3 (CPOL=1)

- Supports SDR, DDR, DUAL, DUAL I/O, DDRDUAL I/O, QUAD, QUAD I/O, DDRQUAD I/O modes.

- Supports all the commands mentioned in the CYPRESS spi specification.

- Has assertion and coverage with more than 95% functional coverage.

- Has constraint random test cases to assure the specification is thoroughly met.

- Supports all possible frequencies mentioned in the specification

- Supports optional data masking feature.

- Supports optional data masking feature.

- Supports 1s-1s-1s and 8D-8D-8D mode and dynamic mode between them.

- Supports a wide variety of Dynamic as well as Static Error Injection scenarios

Deliverables

- SPI slave flash memory Model

- SPI Monitor & Scoreboard

- SPI MASTER BFM/Agent

- Test-Bench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests and Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Notes