CXL 2.0 Verification IP

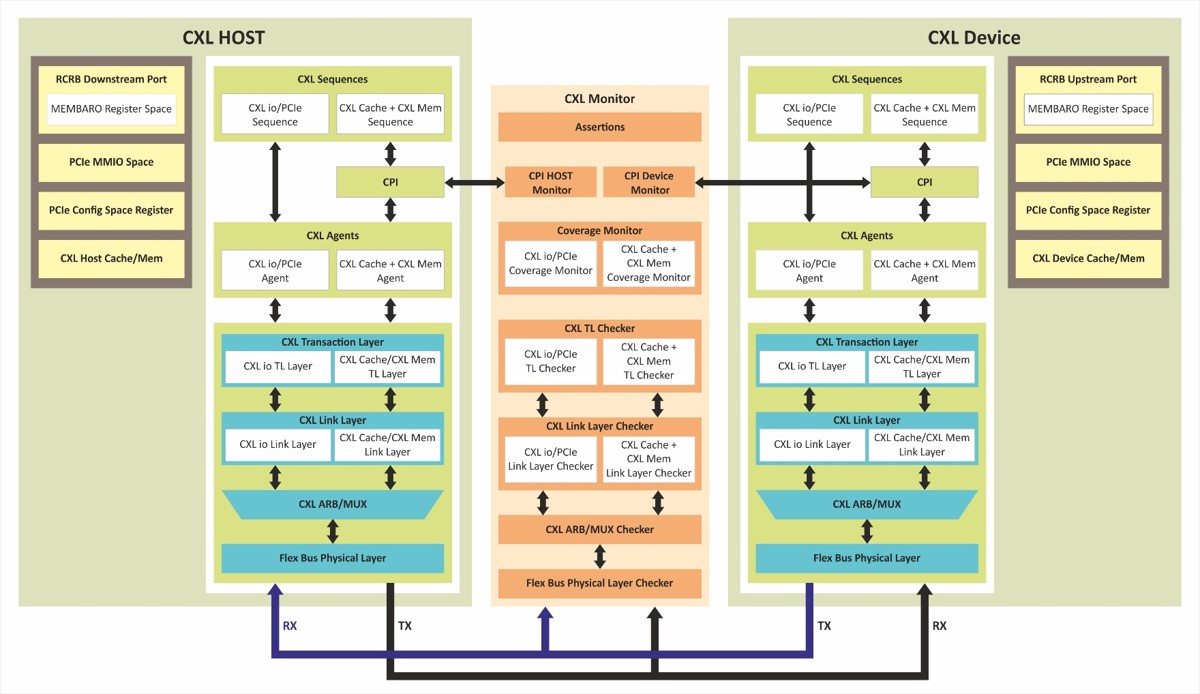

Truechip's CXL 2.0 Verification IP provides an effective & efficient way to verify the components interfacing with CXL interface of an IP or SoC.

Truechip's CXL 2.0 VIP is fully compliant with the latest CXL specifications. This VIP is lightweight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment.

Features

- Compliant with the CXL 1.1 and 2.0 specifications.

- Verification IP configurable as CXL Host and Device when operating in Flex Bus mode and as PCI Express Root Complex and Device Endpoint when operating in PCIe mode.

- Support for all three CXL protocols i.e., CXL.io, CXL.cache, CXL.mem, and device types to meet specific application requirements with user-configurable memory size for both CXL Host and Device.

- Support for CPI(CXL-Cache/Mem Protocol Interface).

- Support for Alternate Protocol Negotiation for CXL Mode.

- Support Pipe Specification 5.1 with both Low Pin Count and Serdes Architecture.

- Support for CXL ALMP transmission and reception to control virtual link state machine and power state transition requests.

- Support for CXL ACK forcing and Link Layer Credit exchange mechanism.

- Support Arbitration among the CXL.IO,CXL.cache and CXL.mem packets with Interleaving of traffic between different CXL protocols.

- Support for randomization and user controllability in flit packing.

- Support for CXL Link Layer Retry Mechanism.

- Support for Configurable timeout for all three layers.

- Support for different CXL/PCIe Resets.

- Support for power management including the low power L1 with sub-state and L2.

- Provides a comprehensive user API (callbacks).

- Built-in Coverage analysis.

Deliverables

- CXL Host/Device

- CXL BFM/Agents for:

- Host and Device sequences

- Phy layer/Flex Bus

- Transaction layer(CXL.IO and CXL.cache, CXL.mem)

- Link layer(CXL.IO and CXL.cache, CXL.mem)

- Arbiter/Mux layer

- CXL Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Tests

- Random Tests

- Error Injection Tests

- Assertion and Cover point Tests

- Compliance Tests

- Integration Guide, User Manual, and Release Notes