CXL 3.0 Verification IP

Truechip's CXL Verification IP provides an effective & efficient way to verify the components interfacing with CXL interface of an IP or SoC. Truechip's CXL VIP is fully compliant with latest CXL specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure the highest levels of quality.

- 24X5 customer support.

- Unique and customizable licensing models.

- Exhaustive set of assertions, cover points with connectivity example for all the components.

- Consistency of interface, installation, operation, and documentation across all our VIPs.

- Provide complete solution and easy integration in IP and SoC environment.

- On-the-fly protocol checking using protocol check functions, static and dynamic assertion.

- Provides a comprehensive user API (callbacks).

- Graphical analyzer for easy debugging, regression analysis, performance, statistics, charts and automatic integration.

Features

- Compliant with the CXL 3.1,2.0, 1.1 specification.

- Support Pipe Specification 6.2

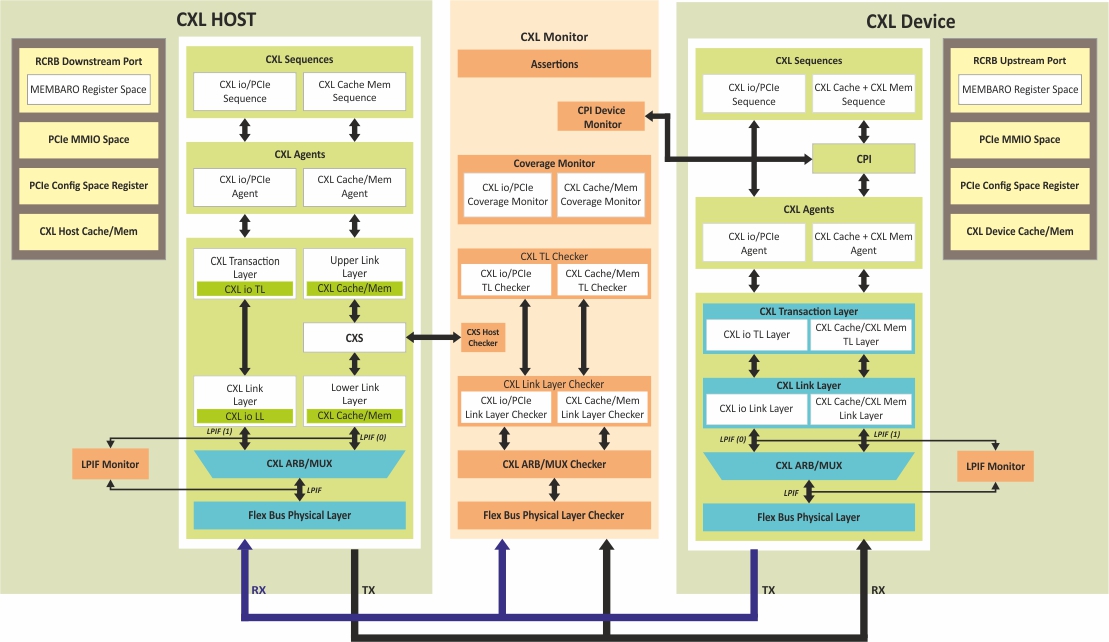

- Verification IP configurable as CXL Host and Device when operating in Flex Bus mode and as PCI Express Root Complex and Device Endpoint when operating in PCIe mode.

- Support for all three CXL protocols i.e., CXL.io, CXL.cache, CXL.mem and device types to meet specific application requirements with user configurable memory size for both CXL Host and Device.

- Support for CPI v1.0 (CXL-Cache/Mem Protocol Interface), CXS B (Credited eXtensible Stream), LPIF v1.1 (Logical PHY Interface) and PIPE v6.2 .

- Support for Alternate Protocol Negotiation for CXL Mode.

- Supports SerDes PIPE Architecture as well as Original PIPE Architecture.

- Supports Low Pin Count Interface as well as Legacy PIPE Interface.

- Configurable PIPE width support:

- Original PIPE Arch. - 8, 16, 32, 64

- SerDes PIPE Arch. - 10, 20, 40, 80

- Support for block level verification.

- Support for CXL Retry Mechanism.

- Support for 68B and 256B flit structure.

- Support for Configurable timeout for all three layers.

- Support for different CXL/PCIe Resets.

- Support for CXL 3.1 Configuration and Memory Mapped Registers (For CXL Device and Ports).

- Support for CXL ALMP transmission and reception to control virtual link state machine and power state transition requests.

- Support for CXL ACK forcing & Link Layer Credit exchange mechanism.

- Support Arbitration among the CXL.IO, CXL.cache and CXL.mem packets with Interleaving of traffic between different CXL protocols.

- Support for randomization and user controllability in flit packing.

- Support for 256B flit in 64GT/s with PCIe Gen6 as well as 32/16/8 GT/s speeds with backward compatibility.

- Support for power management including the low power L1 with sub-state and L2.

- Provides a comprehensive user API (callbacks).

- Built in Coverage analysis.

- Support for CXL in band control message with CXL 3.1. (Viral & Poison)

- Provides two types of 256B flits mechanism (Standard 256B flit & LOpt 256B flit).

- Support for Credit exchange field within 256B flit.

- Provides two types of routing mechanism. (HBR and PBR).

- Support all 3 coherency models HDM-D, HDM-H and HDM-DB to access HDM memory.

- Support PBR TLP for cxl.io

- Support for Back Invalidate transactions.

- Support for RAS error logging.

Deliverables

- CXL Host/Device

- CXL BFM/Agents for

- Host and Device sequences

- Transaction layer(CXL.IO and CXL.cache, CXL.mem)

- Link layer(CXL.IO and CXL.cache, CXL.mem)

- Arbiter/Mux layer

- PHY layer

- CXL Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Cover Point Tests

- Compliance Tests

- Documents:

- Integration Guide

- User Manual

- Quick start Guide, Release Notes

- FAQs